Part Number: ADS1299

When I trying to connect to ADS1299 with STM32 there is strange behavior:

I can't read registers after normal sequence of SDATAC and read commands.

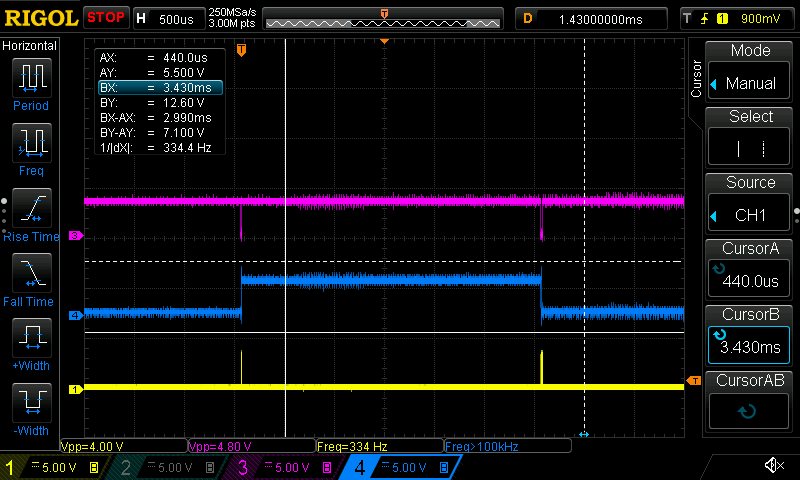

I checked all signals on the line, timings tssc - its was normal, but ADS1299 always receive "0".

After some tryes I found that after write sequence for SDATAC before pushing high CS line I need to add delay or this command ignored.

I don't find description of this behaviour in documentation ("The SDATAC command cancels the Read Data Continuous mode. There are no SCLK rate restrictions for

this command, but the next command must wait for 4 tCLK cycles before completion." and same for multibyte command). Of course, I added this delay between SDATAC and registers reading, but this don't work.

If this proper ADS1299 operation and this will be the same for all single-byte write commands or my controller works incorrect ?