Hi,

I would like to confirm regarding the serial interface, so could you please give me your comments ?

Q1.

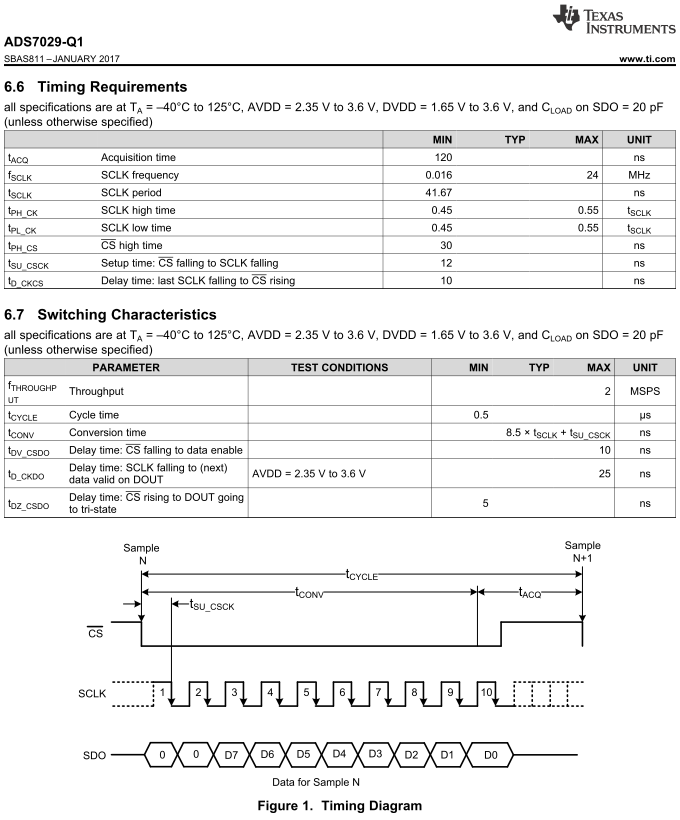

Is my understanding correct that SDO becomes "0" when /CS falls and SDO remains "0" until SCLK falls ?

Q2.

Is my understanding correct that the rising edge of SCLK is used when capturing data with FPGA since SDO data is switched in synchronization with the falling edge of SCLK after /CS signal falls ?

Q3.

Is my understanding correct that zero data of 2-bit is always added to the output data as a dummy bit ?

Q4.

Is my understanding correct that D0 from SDO is output at the 9th falling edge of SCLK ?

Q5.

Does SDO hold D0 even if the 10th SCLK fall ?

Q6.

Does SDO hold D0 even if the 11th SCLK fall ?

Q7.

Is D0 held until /CS goes high ?

Q8.

Can SCLK is kept high when /CS is low ?

Best regards,

Kato