I'm using the ADC12DJ5200RF-EVM Rev B in JMODE3 to interface with a Stratix 10 FPGA. The receive side of the JESD link uses Intel JESD204B IP, which has worked when I used the ADC12DJ3200-EVM. I've gotten the link up, with K = 20, but I see bad data mixed with expected samples.

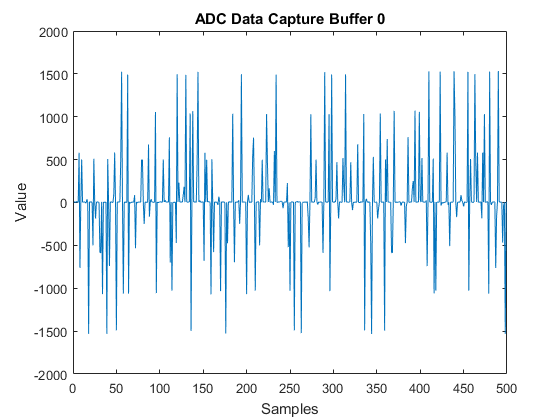

The images below show the data stream at the output of the Intel JESD204B Receiver IP, at the link clock rate, before (jesd_link_*_data) and after (tpl_data_*_out) the transport layer. These images were captured with no input stimulus, so I'd expect values near zero.

Signal Tap, pre and post transport layer:

Plotted, post-transport layer:

I'm thinking that maybe my external sample and reference clocks are bad, but both share a common 10 MHz reference and look mostly clean on a spectrum analyzer. My sample clock is 9 dBm and reference clock is 6 dBm. I'm not sure why this is happening, could it be the JESD204C protocol has extra alignment words periodically sent around the data?

Thanks,

Ryan