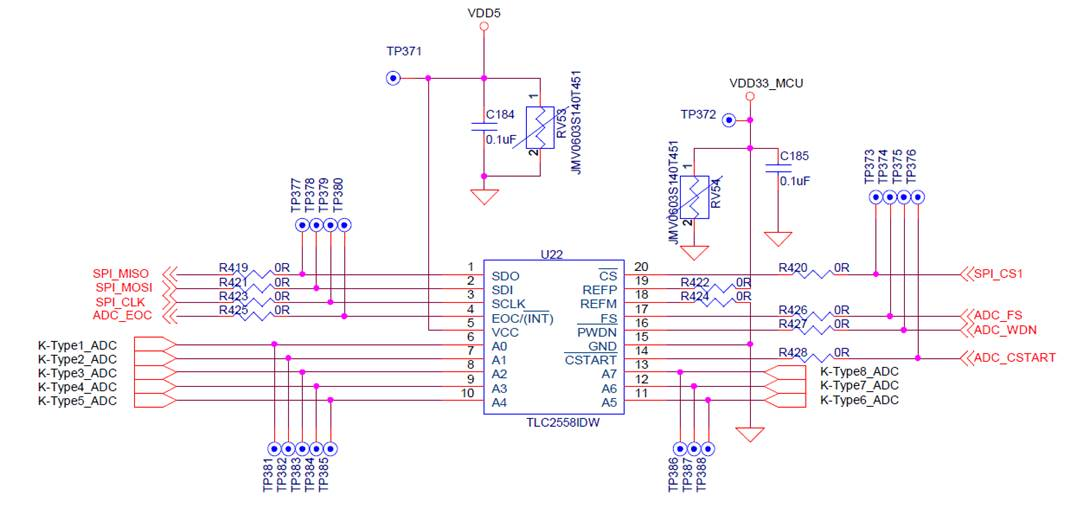

Hello, we have a project using Atmel ATSAM4E8E platform to drive TCL2558 ADC converter.

Now we can't use it even we follow the datasheet to set.

we are according to datasheet to building whole read process,

But we can’t successful read ADC value in below process.

Step as below:

1. Writing 0xA0C0 to setting mode is sweep mode.

2. written 0x9000 to read CFR register value

3. start convert by pull down CSTART

4. waiting for INT pin trig

5. written 0xE000 to read FIFO data

In step 2, we can;t to read CFR data successful after write 0x9000 command.

We tried to read single ADC value (one shot mode),

Step as below:

1. written 0xA000

2. written 0x9000 to read CFR register value

3. start convert by pull down CSTART

4. waiting for INT pin trig

5. read ADC value and write next ADC channel if you want read.

Same with sweep mode, the interrupt had no occurred, we don’t know what we are ignore some things in above steps.

We tried to read and write data when SCLK falling edge

But we have no read any value on SPI bus,

And we written data when SCLK rising edge, the SPI receiver had value, but it is different with write data.

So we are confusing in this timing diagrams, when did the SPI trig?

If we use "one shot" to read ADC, could we ignore to write CFR?

Thanks,

Best Regards,

Johnnie