Setup - Xilinx ZCU102 directly connected to ADS54J66EVM on HPC1.

JESD parameters -

Subclass 1, LMFS = 4421, K = 32, RefClk = 153.6MHz, RxCoreClk = 76.8MHz, Line Rate = 3.072 Gbps, Sysref = 3.2MHz

ADS54J66 parameters -

Sample Clk = 153.6MHz, DDC mode = 8 (direct sampling)

Fin = 644MHz at 10dbm

ADC config sequence

ADS54Jxx_ANALOG

0x00 0x81

0x8020 0x00

0x8021 0x00

0x8022 0x00

0x8026 0x00

0x8053 0x80

0x8055 0x00

ADS54Jxx_DIGITAL

0x6800f7 0x01 //digital top reset self clearing

0x680000 0x01 //reset digital page 6800h

0x680000 0x00 //clear digital page reset

0x690000 0x80 //CTRL K

0x690001 0x01 //JESD mode 20x

0x690002 0x00

0x690003 0x00

0x690005 0x00

0x690006 0x1F //K 32

0x690007 0x08 //subclass 1

0x690016 0x00

0x6A0016 0x02 //PLL mode 40x

0x614100 0x08 //mode 8

0x614101 0x00

ADS54Jxx_LOWLEVEL

0x4003 0x00

0x4004 0x00

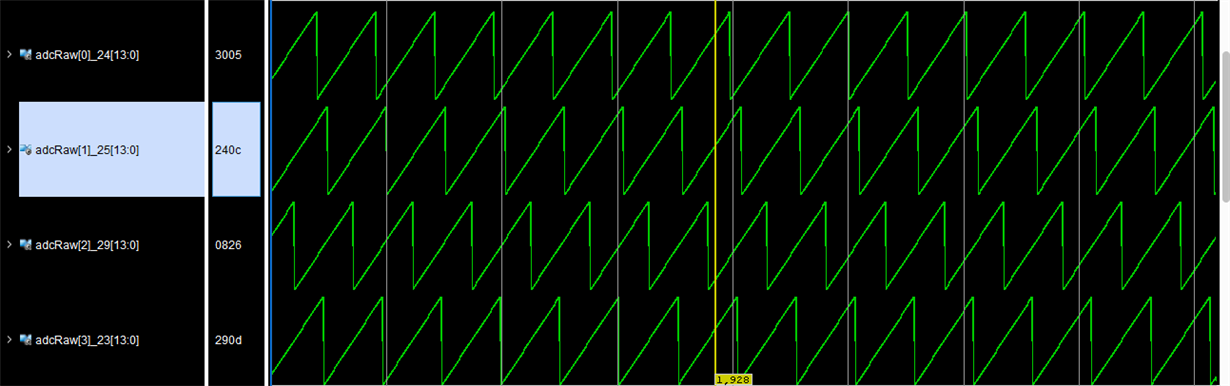

The ADC raw sample data does not look like a sine wave. I have connected output from a signal generator to ADC inputs A, B and C though a splitter whereas input D is left disconnected.

I tried the built-in test patterns in the ADC and was able to see correct ADC sample data for ramp pattern and toggle pattern. While in testmode I disabled interleaving engine 0x680018 (write 0x03) and DC correction 0x0x680068 (write 0x06).

I can also see the ADC lanes are not synchronous, there is a slight phase offset between them. Is the configuration sequence and the setup I am using correct ?