Other Parts Discussed in Thread: ADS54J66EVM, , ADS54J66, DAC37J82, LMK04828, DAC5675A, DAC38J82

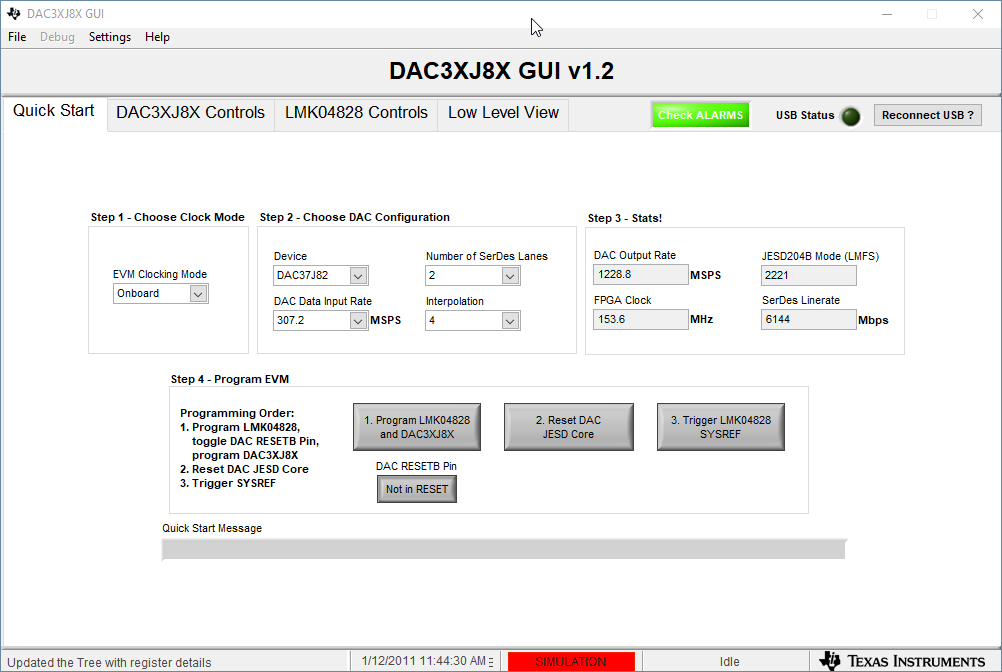

Setup - ZCU102 connected to ADS54J66EVM on HPC1 and DAC37J82EVM on HPC0.

ADS54J66 parameters - LMFS = 4421, K = 32, 307.2MSPS, Line rate = 6.144Gbps, Sysref = 2.4MHz, Mode 8 (bypass DDC), VCO 0 = 2457.6MHz

Input Frequency - 70MHz on all 4 ADC channels

FPGA RX JESD - 4 lanes, Refclk = 153.6MHz, Coreclk = 153.6MHz, CPLL, LIne rate = 6.144Gbps

FPGA TX JESD - 8 lanes, Refclk = 153.6MHz, Coreclk = 153.6 MHz, CPLL, Line rate = 6.144Gbps

DAC37J82 parameters - ?

I'm looking to set up a loopback where the incoming real sample data from 4 channels of ADS54J66 is sent to either 1, 2 or all 4 channels of DAC37J82. The real sample data sent to DAC does not necessarily have to be for all 4 channels. It can only be for 1 channel (either A, B, C or D). eg - ADC channel A to DAC channel A.

I'm setting this up to test the JESD interface between FPGA, ADC and DAC and get familiar with the data converters.

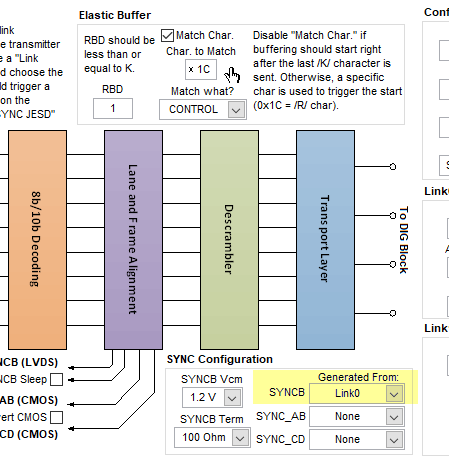

I'm using a 128 in, 256 out FIFO in between JESD RX and TX module. I have set up the FPGA JESD TX module for 8 lanes only because DAC37J82 has 8 lanes, but if less lanes are used (LMF 222 or 421), the remaining bits on the 256bit AXI Stream bus are set to zero.

Could you please confirm this setup and suggest a configuration for DAC37J82. Do I have to synchronize the LMK04828 chips on the DAC and ADC EVM with an external reference clock ? Thank you