Other Parts Discussed in Thread: INA317, , OPA314

I have watched videos and read articles about how to drive SAR A/D converters but there is only minimal information regarding Sigma-Delta converters.

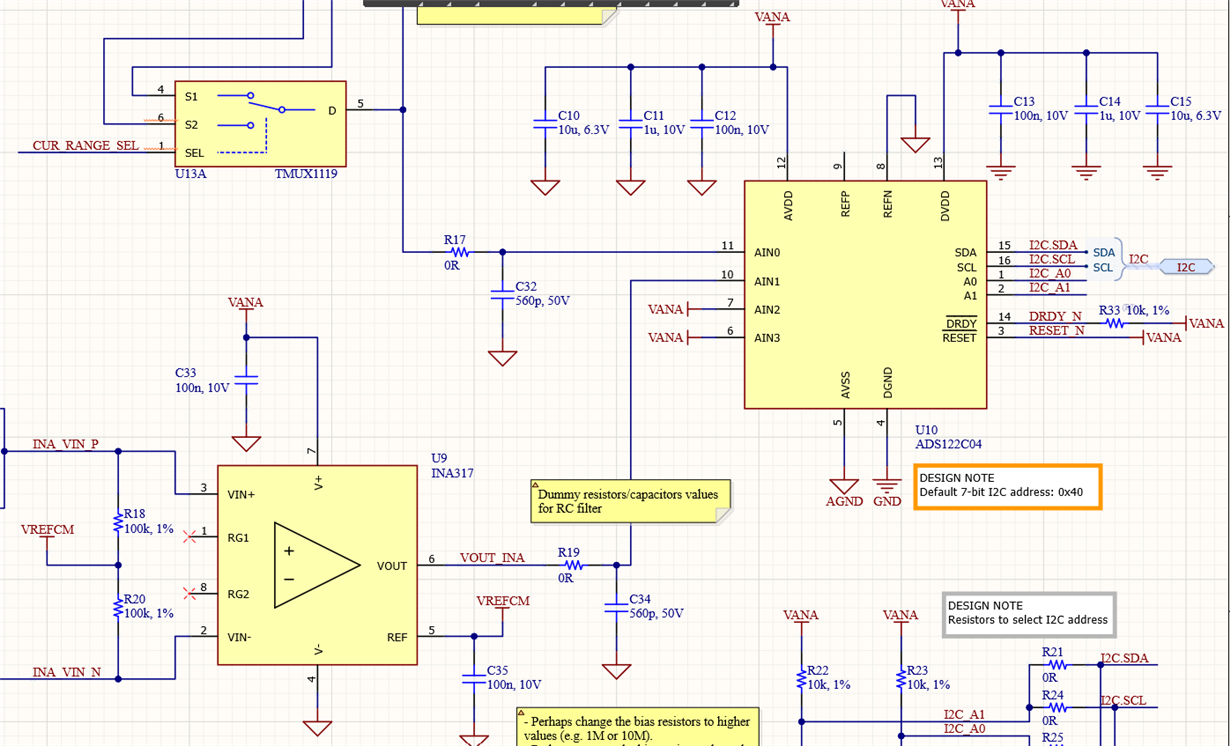

In my application I want to drive an ADS122C04 converter with an INA317. What recommendations should I user for this case?