Other Parts Discussed in Thread: THS4511, ADS54J60

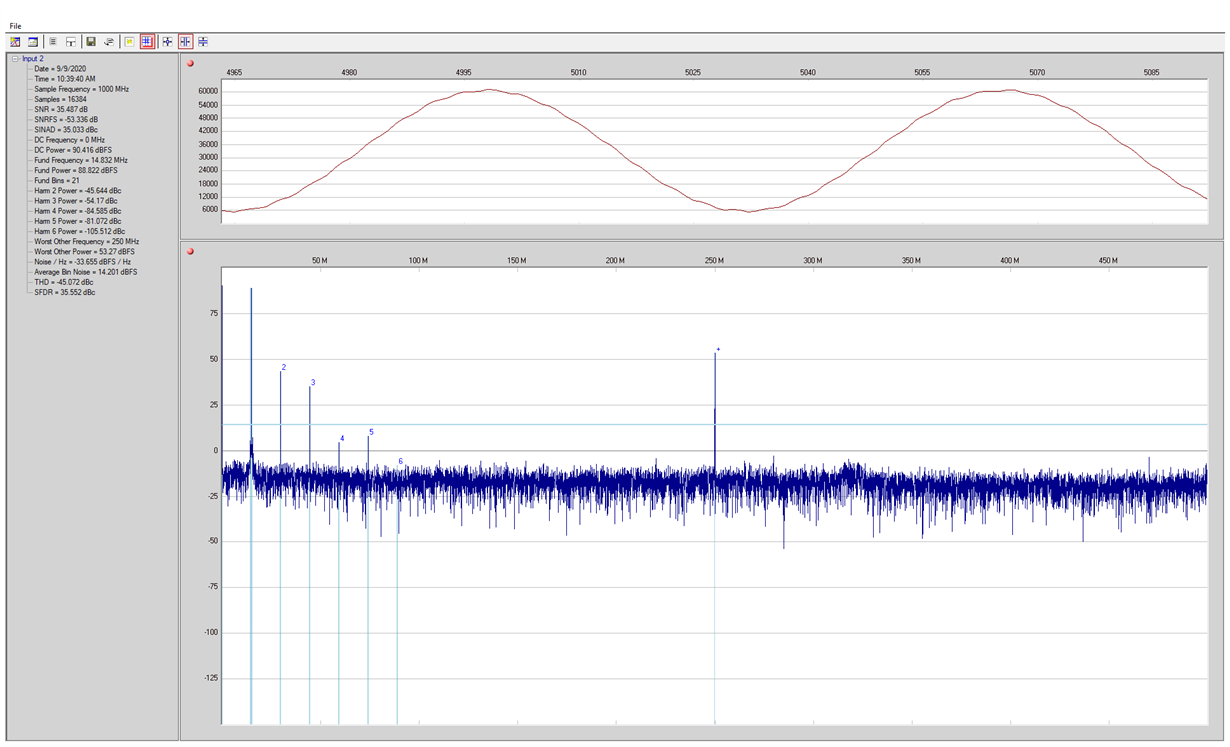

Hello, I have prototype board with ADS54J40 which is connected to the FPGA via FMC+ connector using 8 lanes. Unfortunately one of lanes is connected to wrong FMC+ pin so I am using ADC in 4 lanes mode. JESD is working and I can receive correct data, but there is always 250 MHz in signal frequency spectrum (even with unconnected inputs) which is quarter of the sampling frequency 1 GHz. We tried to change it to 900 MHz which results in parasite frequency of 225 MHz (again one quarter of the sampling frequency).

On ADC board there is nothing what would generate this frequency. After some elaboration we found out that there is something going on on unused JESD lanes with exactly quarter of sampling frequency. As ADC is in 4 lanes mode I supposed that unused lanes should be powered down but they either aren't or something else is going on.

Thank you in advance for your suggestions.