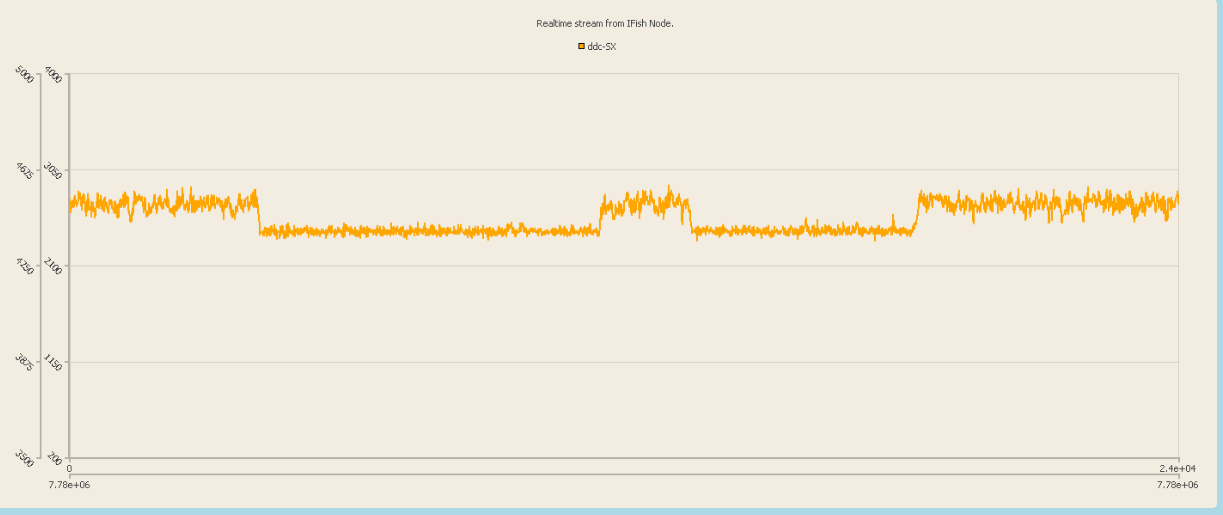

We have a product with a DDC118. Some units shows a behavior where the zero offset level starts at a level and after a period of time start to jump up to a new level. During a transition time the level makes jumps up and down between the levels and after more time the level stabilizes at the upper level. 2 out of 10 units show this behavior. The device is supplied with 5V, 3.3V and 4.096 reference and I can not see any strange on these supplies. The timing requirements for all clocks are fullfilled. The device is clocked at 19.2MHz.

Is this any known issue? See attached graph.