- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

TLC2558 datasheet specify from SCLK rising edge to SDO valid, td(CLK-DOV), when FS=1.

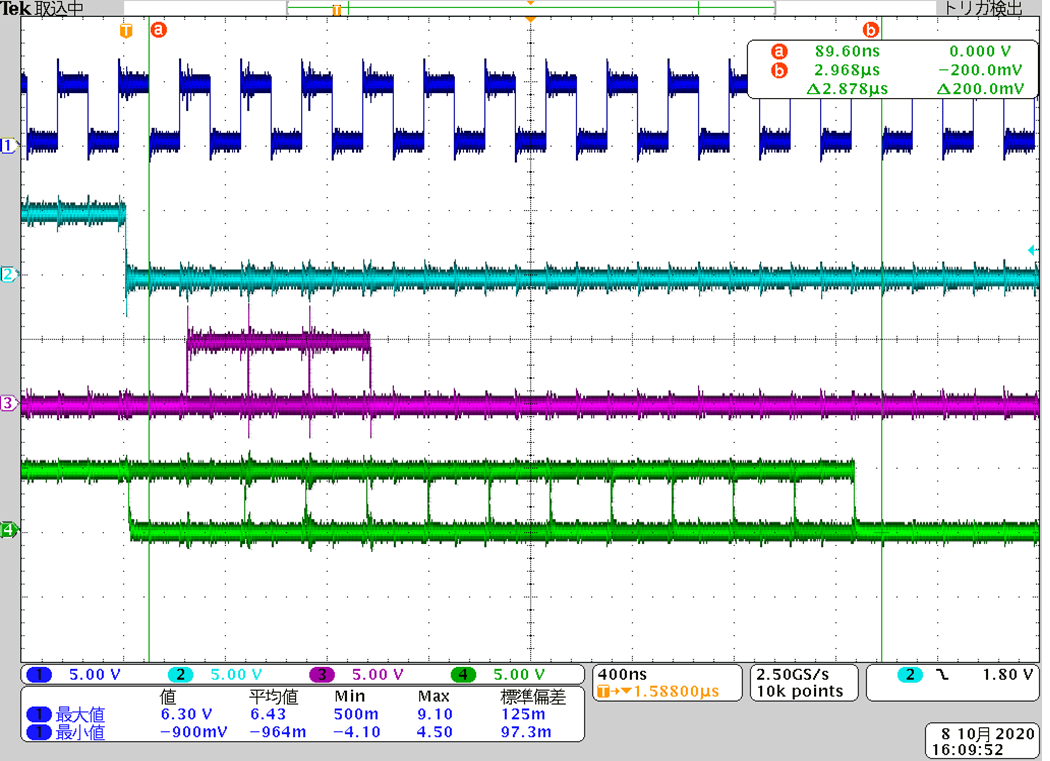

However, my customer captured SPI waveform when FS=1 as follows. (Ch1=SCLK, Ch2=CS, Ch3=SDI, Ch4=SDO)

It appears that SDO get valid at SCLK falling edge, not rising edge specified in the datasheet.

Is the datasheet wrong?

Best regards,

K.Hirano

Hi Hirano-san,

How are you controlling the FS input on the TLC2558? Is it static or controlled through a GPIO? Also, can you re-capture that waveform with a faster (20MHz ideally) SCLK?

Tom,

Thank you for your response.

FS input is always HIGH, static.

My customer re-captured waveforms with 10MHz SCLK as attached .xlsx file.

The SIO changes at SCLK rising edge.

EAM1_TLC2558.xlsx

Best regards,

K.Hirano

Thank you Hirano-san,

The serial data out from these devices is pre-released by ½ clock cycle, plus a delay. What this means is that while valid output data is available on the rising edge of SCLK, the rising edge also triggers the next data bit. With low clock speeds, it may appear as if data is changing when it should be valid. As you increase the SCLK speed towards 20MHz, it should begin to look like the data changes on the falling clock edge.

Tom,

Thank you for your response.

However, datasheet figure 19 does not show what you are mentioning, it shows SDO gets valid after the delay at SCLK falling edge, not rising edge as you are mentioning. This confused my customer.

Please correct the datasheet at the next timing TI revise it.

Best regards,

K.Hirano