Hi, TI

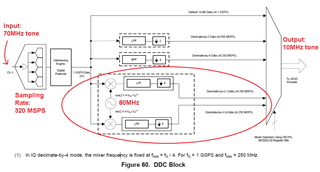

We are using ADS54J60 with the following configuration parameters (see attached image):

- DDC block configuration: Decimate-by-4 with IQ Outputs.

- Sampling Rate: 320 MSPS.

- Mixer frequency (Fixed at Sampling Rate/4): 80 MHz.

- Register 44h of Main Digital Page (6800h): DIGITAL GAIN = 0h.

We are injecting a 70MHz tone into the analog input of the ADCs and when we plot the acquired data we successfully obtain a 10MHz but with half the amplitude of the 70MHz tone. RF generator output is matched to 50 Ohm.

We believe that the reason may be given by the fact that quadrature demodulation causes the amplitude at the output of each component to be divided by 2.

Could you please clarify whether or not the DDC block compensates for this loss of amplitude or do we need to compensate manually writing some value on DIGITAL GAIN field of register 44h in the Main Digital Page. We could not find this information in the datasheet (SBAS706D).

If the DDC block, by default, already compensates for this amplitude loss, could you give us some advice about what could be happening?

Best regards,