Other Parts Discussed in Thread: DLPC4420, DLP780TE, DLPA300,

Tool/software:

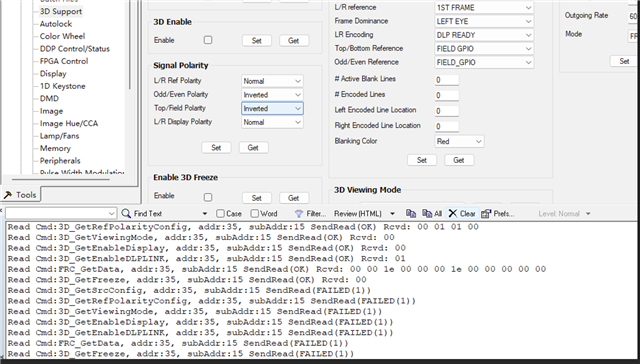

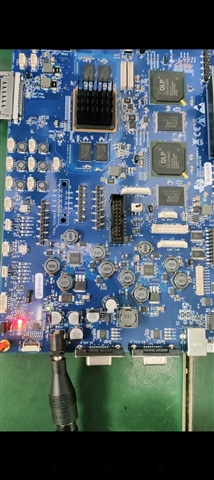

hello, I followed the user manual instructions to set up the system, but I am encountering a critical issue during operation. and I am encountering the same question 。How solution at the fina?(TheDLPC4420AEVM board is purchased not long ago.i used this board first time.

Issue Description:

- When I power on the DLPC4420EVM, the USB device appears for a few seconds and allows me to communicate with the DMD via the DLPC44xx GUI.

- However, after a few seconds, the screen goes black, the USB device disappears from Windows Device Manager, and I lose all control over the DMD.

- During the short period when USB is active, I am able to load test patterns and make adjustments, but as soon as the USB disconnects, the DMD stops displaying any content.

- The issue persists even when using different power supplies and USB cables.

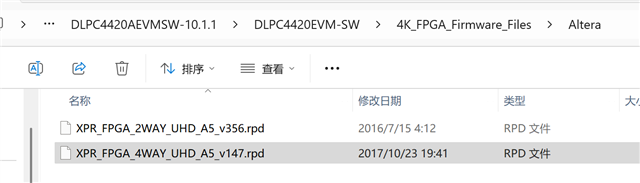

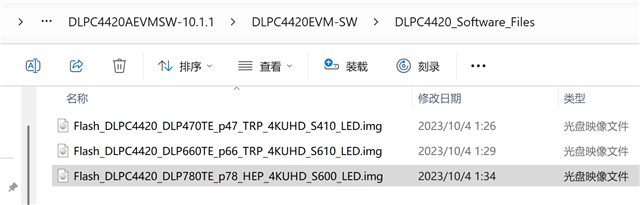

- I have already reflashed the firmware multiple times using

Flash_DLPC4420_DLP780TE_xxx.img, but the issue remains the same.