Dear,

Could someone give me your advise for following?

Related post:

http://e2e.ti.com/support/dsp/tms320c5000_power-efficient_dsps/f/109/t/183979.aspx

Device: TMS320VC5507ZHH

I just want to confirm my understanding:

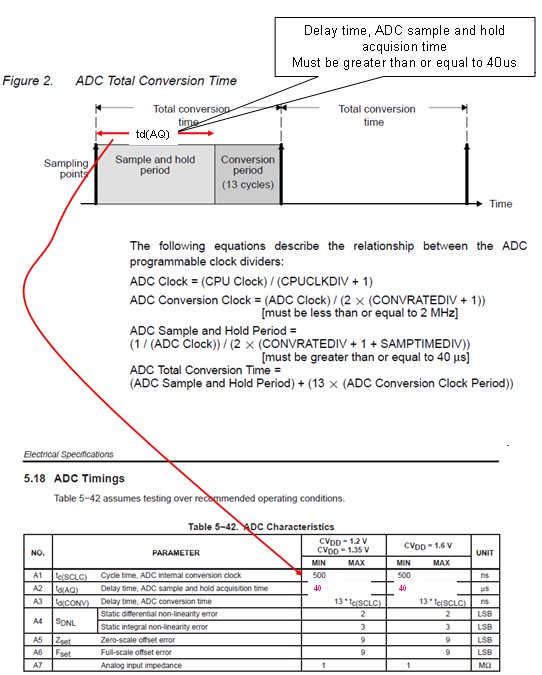

Page 130 Table 5-42 in TMS320VC5507 Data Manual(sprs244j), ADC Characteristics says,

td(AQ) Delay time, ADC sample and hold acquisition time MAX=40us.

On the other hand, TMS320VC5507/5509 DSP ADC Reference Guide(spru586b), says

ADC Sample and Hold Period = (1/(ADC Clock)) x (2 x (CONVRATEDIV + 1 + SAMPTIMEDIV))

[must be greater than or equal to 40us]

My Question :

I think spru586b is right.

If so, I think the td(AQ) should be MIN=40us, not MAX, in datasheet sprs244j.

Am I right?

Regards,

Okayama