Hi All:

The problem about connecting C6678 core0 on our custom board has been solved after we modified the reset process.But there are some other problems.Firstly, we are not sure the connecting state is whether right or wrong.And we still cannot inialize some interfaces e.g. DDR and SPI.

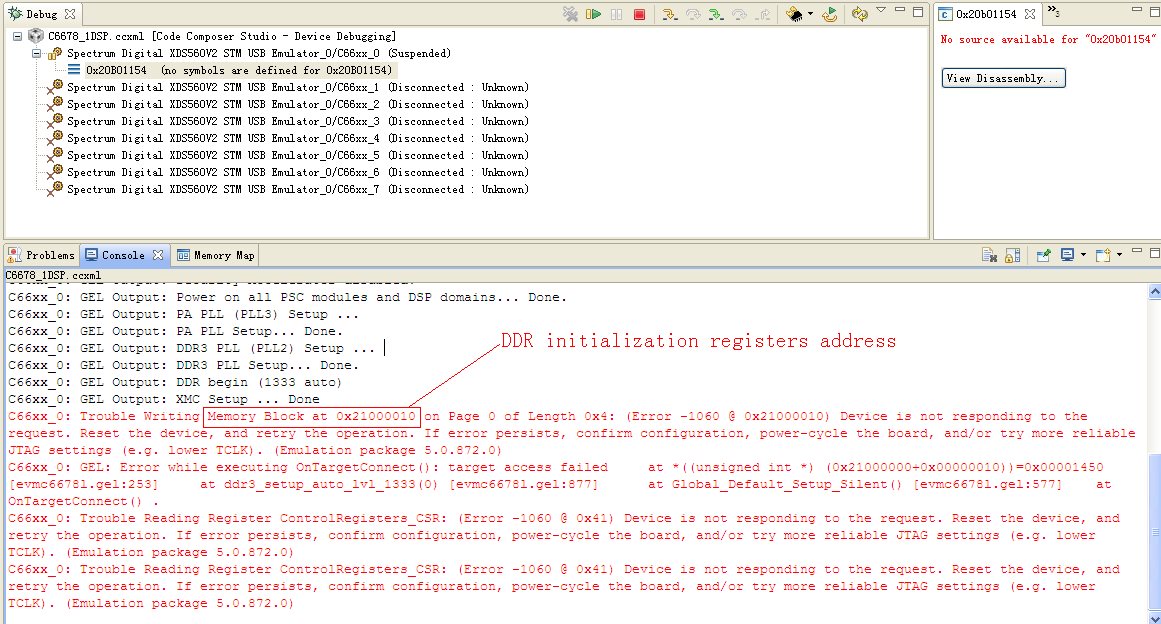

1.this is the state we successfully connected core0,but we are not sure it is right or wrong

2.we read some state registers after we connected core0, and the value of address 0x023100e4 is different from what is read from our normal board.What does the value mean?Is it related with our errors?

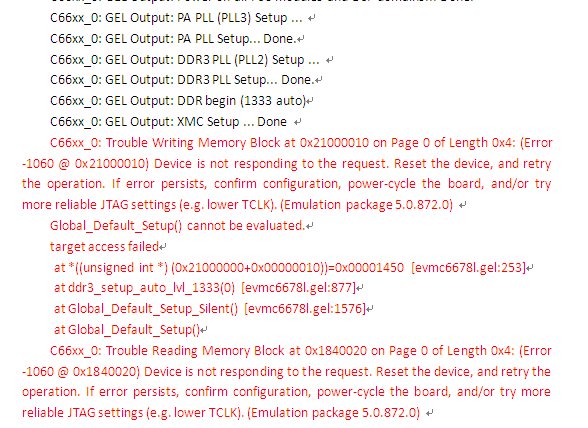

3.When we initialized SPI or DDR,the errors come.What does it mean?

4.By the way ,when we debug using "run to line" ,it pop-up a dialog as follows.What does it mean?We did not use gel files,so where is the GEL application?

5.The word file is the result we run the gel file alone on the abnormal board and a normal board.Though the parameters are not entirely match with our board,it should not go to dead. Is it possible the chip is bad?

Eagerly awaiting your reply !