- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

In a related question, I was informed that you will release C code to control the EVM board programmatically by the end of the year (2024).

What's the status on this? I don't see anything online.

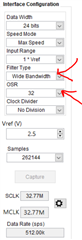

Furthermore, I see that from the GUI that I can manipulate the sampling rate down to 8kHz. But this is done by using the Clock divider in the internal interface to Div/16 and then by also dividing the external clock (EVM CLK) by a factor of 2 (or the opposite, 16 in the External clock and 2 in the clock divider in the internal interface option).

How can I do that programmatically? I am interested in a sampling rate <32kHz which requires a division of both clocks. I have checked the github repository for the ADS127L11EVM board (previous version), and there is no mention of an external clock, at least up to my understanding of the code.

Kind regards,

Vasilis

Hi Vasilis G,

You can now access our firmware on github: https://github.com/TexasInstruments/precision-adc-examples/tree/main

The ADS127L21 code is there under "devices"

Also I am not sure what you mean by the issue with reducing the clock speed? The L21 by default supports many output data rates (ODR) <32kSPS using the 32.768 MHz clock on the EVM. See Table 7-7 for the wideband filter and Table 7-9 for the sinc filter.

Please let me know if I have missed something with your question

-Bryan

Hi Bryan,

I probably didn't explain it very clearly before, excuse for this.

I'll give you an example from the GUI.

In order to reduce the Sampling speed there are 2 options.

1. Under the Interface configuration, there is a clock divider. There you can divide the clock by a maximum of 16 times. 512ksps/16 = 32ksps. What this does, is basically changing the CONFIG2 register value to the desired one, which can also be done via a custom script.

2. Then, if I want to reduce the sampling speed even further (<32ksps), I need to press the gear button (bottom left) and use another clock divider. The source of that clock is stated to be the EVM. Then I check the register map config and no register values are changed there. So the question arises. How do I control the EVM clock via a custom software? Are there any sample codes for this? Functions or directions? Am I possibly missing something?

Kind regards,

Vasilis

Hi Vasilis G,

Thanks for clarifying. My point is that the ADC has many programmable OSRs that further reduce the data rate without having to scale the external clock. These are shown in the tables I mentioned in my last post

The OSR and filter selection are set using the FILTER1 register. I have copied the OSR options below. I have also shown these options in the GUI (second image). Note that when you toggle these values, the Data Rate at the bottom left in the GUI will change, and you will be able to select several combinations that set a data rate <32 kSPS

-Bryan

**Attention** This is a public forum