Other Parts Discussed in Thread: SN65LV1224B, DS25BR110

Hello,

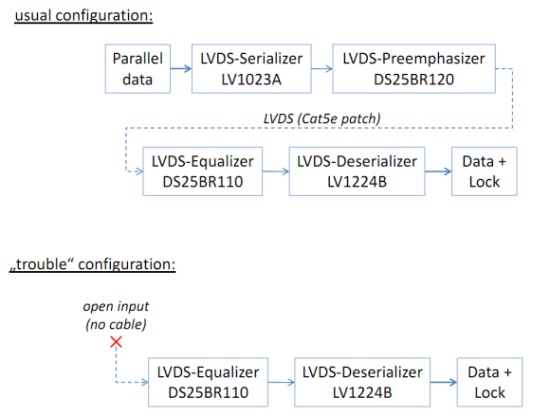

we are currently facing a little hardware problem, including one of your products, the SN65LV1224B LVDS de-serializer. Please find a structural overview in the drawing attached.

The problem is as follows:

In an usual configuration, the data is received correctly, but if no cable is attached to the receiving unit, a "false-lock" occurs and fades spontaneously on the output of the de-serializer, resulting in random false-data on the output of the de-serializer. In this state, it seems that the rate of "lock"- and "non-lock"-time varies depending on the frequency of the reference-clock of the de-serializer (tested 10MHz up to 40MHz) AND the level of equalization of the (National Semiconductor's) DS25BR110. Any way, this is not the behavior we expected. We thought that an open input (no cable) results in a constant inactive "lock" signal and tristate-data.

Could you imagine, that there is a problem with the de-serializer? Maybe we've got a wrong configuration? What do you think?

It is worth to note, that

- the NSC's DS25BR110 receive buffer is located closely on-board to Texas Instruments' LVDS-de-serializer LV1224B and that

- there are 6 similiar receiving units on the board next to another, each of it may have a cable connected or not (hot-pluggable)

Thanks in advance,

yours sincerely, Harald Schweitzer