DP83867IR: communication problems.

Hi all,

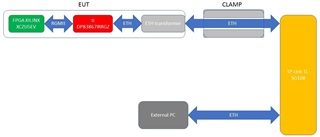

in our machine we have the DP83867IRRGZ as ethernet controller and Xilinx XCZU5EV as FPGA.

We have connect our machine to an external ethernet switch: TP-link TL-SG108 and we have connected a PC to the external ethernet switch. The cable between EUT and ethernet switch pass through the clamp.

During the immunity test we have done a ping command between EUT and external PC, at 1Gbps.

The immunity test was EN 61000-4-4 (burst level 0.5kV (repetition freq. 5kHz), CLAMP on Ethernet cable).

When we apply the burst, the ethernet connection fails, when the burst stops the ethernet connection is restored.The same test @10/100Mbps ends successfully.

If we increase the voltage to 1kV, the ethernet connection loss the "link" and, at the end of burst, the connection doesn't resumes.

We have done the same test Xilinx eval board (HW-Z1-ZCU104 Evaluation Board(XCZU7EV-2FFVC1156)) and the result is the same: @1Gbps, when we apply the burst, the eternet connection falls.

Have you any suggestions in order to increase the noise immunity?

Thanks in advance,

Diego.