dear,

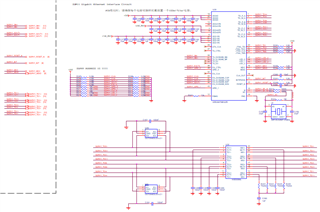

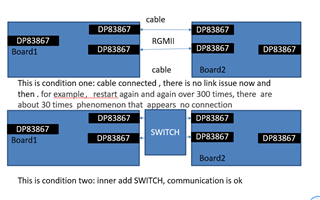

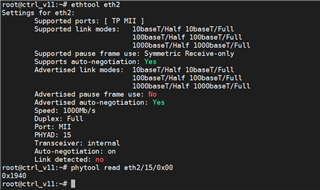

I use network cables to link the both DP83867 board (PING each other ), there is a certain probability of no link phenomenon; for example,restart again and again over 300 times, there are about 30 times phenomenon that appears no connection , the issue is same in RGMI or SGMI interface, and the both DP83867 PCB of boards are same, the schematic is as below, I use 3 channel power supply for PHY chip,that is VDDA1P8 ,VDDA1P0,VDDA2P5, the timing :VDDA1P8 is 200ms earlier than VDDA1P0 and VDDA2P5;

however, I tried to add a switch both the DP83867 board, it is ok,no problem,other operation environment including clock are not changed; could you help me analyze what is wrong with it ?