Other Parts Discussed in Thread: SN65DSI85, SN65DSI83

What is line time on the SN65DSI83, SN65DSI84, and SN65DSI85?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

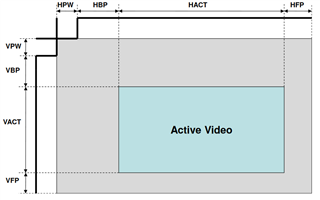

Display panel timing consists of two main parameters: frames and lines.

A frame includes the entire display area and is composed of multiple horizontal lines. At the end of each line, a HSYNC pulse (consisting of a front porch: HFP, a back porch: HBP, and width: HPW) signals the beginning of a new line. This continues until the end of the frame, where a VSYNC pulse (also consisting of a front porch: VFP, a back porch: VBP, and a width: VPW) signals the beginning of a new frame.

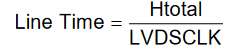

The “line time” is simply the amount of time it takes for the transmission of a line to be completed. In other words, it represents the amount of time between two consecutive HSYNC pulses (or a VSYNC pulse to the next immediate HSYNC pulse). On the output of the SN65DSI83, SN65DSI84, and SN65DSI85, the line time (in microseconds) can be calculated as:

where Htotal is the total amount of horizontal pixels, and LVDSCLK is the frequency of the LVDS clock in MHz. For example, if Htotal = 1054 and LVDSCLK = 70.6 MHz, then the line time is 14.92 us.

On the DSI side, the definition of the line time is the same:

It is the amount of time between two consecutive HSYNC pulses (or a VSYNC pulse to the next immediate HSYNC pulse).

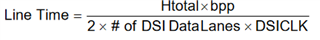

The equation for the line time (in microseconds) is different on the DSI side though:

where Htotal is the total amount of horizontal pixels, bpp is the bits per pixel (either 18 bbp or 24 bpp), and DSICLK is the frequency of the DSI clock in MHz. For example, if Htotal on the DSI side = 2108, bpp = 24, DSICLK = 423.6 MHz, and there are 4 DSI data lanes, then the line time on the DSI side is 14.92 us.

For correct operation of these devices, it is critical that the line time on the DSI side exactly matches the line time on the LVDS side. This is because these devices do not realign any of the timing. For DSI to LVDS conversion to work properly, the timing must be aligned.

For more information on correctly configuring these devices and debug steps for potential issues , please reference the below FAQs: