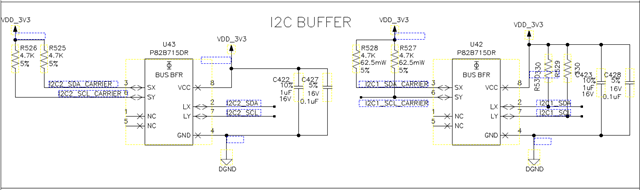

Part Number: P82B715

Hi Team ,

Please review the attached schematic of I2C level translator.

Pull-up of value 10k has been added on I2C2_SDA in other section of circuit .

Each I2C bus has 4 slaves --- ( 2 before buffer and 2 after buffer).

Thanks,

Manoj