Hi Team,

There is a good new that DIN TCAN1042DQ1

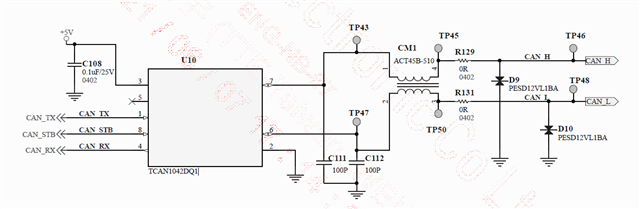

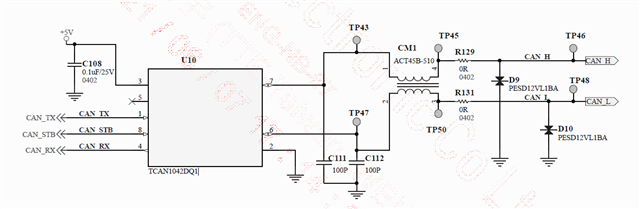

1. I want to confirm with you, what is the maximum input current of this IC under normal operation? I want to confirm the specifications of the LDO from my side

2, Please help check this SCH, THX

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

There is a good new that DIN TCAN1042DQ1

1. I want to confirm with you, what is the maximum input current of this IC under normal operation? I want to confirm the specifications of the LDO from my side

2, Please help check this SCH, THX

Hi Kygo,

The maximum current that this device will draw is in the short-circuit case when some fault exists on the bus. However, in most systems this condition will not last more than a few ms before the fault is recognized and communication ceases, stopping the fault current. For normal operation, the dominant state current will be the typical max. Due to the much lower current draw of the recessive state (which the transceiver will be in the majority of the time) the steady-state current draw will be less than half of the average between dominant and recessive state Icc values. If sufficient bulk capacitance is available on the board, the expected steady state load of the transceiver can be expected to be in the 20mA to 40mA range during maximum bus utilization.

For the schematic, I have a few comments. I would recommend moving the bus capacitors (C111 and C112) to the connector side of the CMC for best effectiveness. Generally I recommend against including any passive components between the transceiver and CMC. I would also recommend including footprints for termination resistors, even if this is an intermediate node. This give flexibility in case the system layout changes and termination needs to be placed here. Can you confirm that this is not meant to be an end-node?

Let me know if you have any more questions.

Regards,

Eric Schott