Our system is using DP83867IR with RGMII and it is able to link 1G with 5meter cable.

But it can not link with 100meter cable.

May I have a recommend some registers settings or Hard ware turning?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Our system is using DP83867IR with RGMII and it is able to link 1G with 5meter cable.

But it can not link with 100meter cable.

May I have a recommend some registers settings or Hard ware turning?

Hi Kosaka-san,

I have a few questions:

Regards,

Adrian Kam

Hi Adrian san

1. We are using default settings.

2. We are using CAT5e.

3. We provide our shematics to TI Japan. And we got some feed back.

OSC connection was no good.

May I have a question for 25MHz external clock.

DP83867 has internal clock.

Can we use this internal clock insted of external 25MHz?

BestRegards

Kosaka

Hi Kosaka-san,

Are you referring to the CLK_OUT pin? If so, then you cannot use it as a replacement for the internal clock. The external clock is needed because it provides a reference for all clocking in the device. Without the external clock, none of the internal clocks will function properly.

If fixing the OSC connection does not resolve the issue, feel free to send me the schematic to see if there is anything else wrong, or have your FAE send it to me.

Regards,

Adrian Kam

Hi Adrian san

I informed our schematics and trial result.

May TI help us.

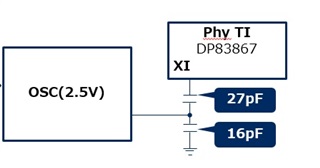

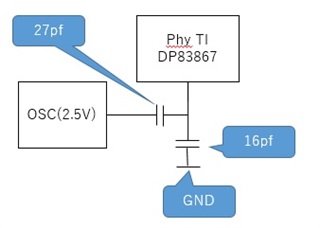

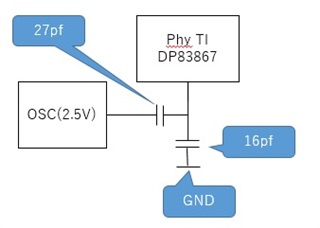

(Step1) Our original OSC connection is below that is not followed the reference design. That is our mistake.

It is not work with 100meter cable.

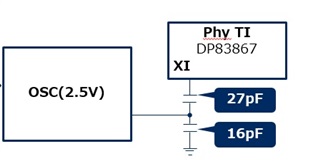

(Step2) We rework the actual board. It is possible to work with 100metor cable.

But it has to make a new Gaber data.

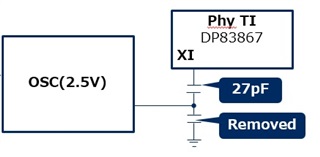

(Step3) We tried below connection. It is possible to work with 100metor cable.

Could we turn these capacitor with this connection?

May TI help us with TI simulation?

Hi Adrian san

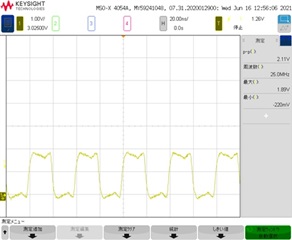

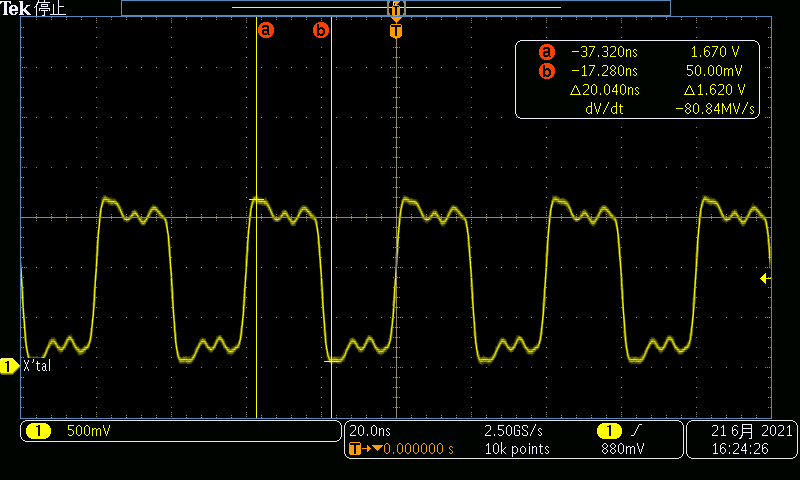

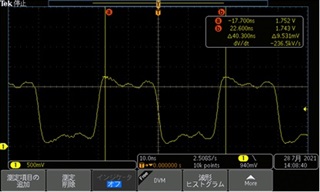

We measure the clock signal at XI with Step3 configuration.

May we use this setting or turning it?

Hi Kosaka-san,

Can you clarify a few things?

Regards,

Adrian Kam

Hi Adrian san

1. Yes. This configuration is not possible to link up with 100m cable.

2. Step2 is following connection. But it need new gaber.

3. Could DP83867IR accept this signal level?

If DP83867IR is not accept this level, may TI simulate these capacitor value?

We are nor clear the Internal ciucuit in DP83867IR.

Hi Kosaka-san,

The connection for step two is correct and the configuration we typically recommend. As a result I would go with this configuration. As for the signal level in step 3, it is too high. The purpose of the capacitors is to divide the voltage of the clock source. With the 16pF removed, the voltage will not be reduced and the clock source will have an amplitude of 2.5V, which is shown in your image. The max voltage level for the XI pin is 2.1V as stated in the datasheet.

Regards,

Adrian Kam

Hi Adrian san

Step1 is meet the spec. But it does not work with 100meter cable.

Is it possible to simulatie the recomend capacitor value for LSI internal logic?

Step2 We will try to increase the capacitor.

BestRegards

Kosaka

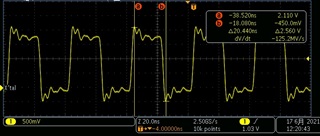

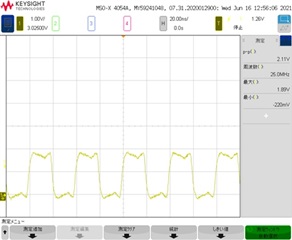

Hi Adrian san

I typo the step number. We tried step3 capacitor value.

We chaged the capacitor from 27pF to 220pF with step3 configuration.

It is possible to link up with 100meter cable.

I attached this clock signal.

Could DP83867IR accept this signal level and load capacity?

Best Regards,

Kosaka

Hi Kosaka-san,

Looking at the clock signal, it seems ok. However, we have not tested the device with the step 3 configuration before. I would suggest thoroughly testing your system to make sure everything else works.

Regards,

Adrian Kam

Hi Adrian-san

Does TI know Why step1 is not working with 100meter cable?

Regards,

Kosaka

Hi Kosaka-san,

The most likely reason is that the configuration in step 1 does not reduce the amplitude of the clock to below the absolute maximum rating. It is not configured like a voltage divider like in step 2. Since it goes beyond the specifications, the PHY will not function properly.

Regards,

Adrian Kam

Hi Kosaka-san,

We have not validated the part with a 220pF for the XI input. As a result, I cannot say for certain that nothing will be affected. Looking at the scope shot, there does not seem to be anything wrong with the clock signal, but you will have to check yourself to make sure everything else is functioning as intended.

Regards,

Adrian Kam

Hi Adrian-san,

When we temporary rework follow recomend connection step2 that conbination is 27pF+16pF

High voltage level is low margin(around 1.5V).So we would like to increase High margin. More higher.

May I have a recommend capacitor conbination?

Regars,

Kosaka

Hi Kosaka-san,

Our recommended combination is 27pF+16pF, and it is with this combination that we have tested the device. If the margin is too low for your board, then you will have to recalculate the values so that the margin is high enough for your board. The capacitors are essentially just a voltage divider, so the values can be adjusted to provide a higher voltage.

Regards,

Adrian Kam

Hi Adrian-san

It seems 27pF+16pF conbination is margin is low. And we do not konw the circuit in the LSI. May TI provide other conbination for high voltage margin?

Reagrs,

Kosaka

Hi Kosaka-san,

Let me consult with my team on this. I can get back to you by Monday at the latest.

Regards,

Adrian Kam

Hi Kosaka-san,

As I have stated before, you will have to find a combination that works for your system, as we have only tested it with 27pF+16pF. You will need to find the combination to meet the XI Input Voltage specs on page 15 of the datasheet. The capacitors are simply a voltage divider to find the optimal combination for 1.8V signaling. Changing the capacitor values should not affect internal circuitry.

In addition, would it be possible to try with a 1.8V oscillator for experiments to confirm the issue is with the XI OSC signal only?

Regards,

Adrian Kam

Hi Adrian-san

Answer1. It is difficult to recalculate these values by ourself. Because we don't have information of internal circuit. The pairs without the calculation become

enormous. May I have the accounting process of 26pF+16pF?

Answer2. Now Our board does not have 1.8V source. Could we use 1.8V OSC when NIC use 2.5V IF?

Answer3. Other Issue 1G compliance signal test is fail after modified 26pF+16pF.

Regards,

Kosaka

Hi Kosaka-san,

Regards,

Adrian Kam

Hi Adrian-san

I would like to reconfirm the Not good reason with step1.

Our mesurement result is meet the spec(VIH,VIL) and reduced.

Which point do you highlight "not reduce the amplitude"?

Does it mean internal circuit in LSI? for out side capacitor value?

Regards,

Kosaka

Hi Adrian-san

1.May I have the formula that is divided it. These circuit is refarence design and I have not experience divided with capacitor.

How TI engineer caluculate 27pF + 16pF?

2. "You can increase the divided voltage by increasing the 27pF cap or decreasing the 16pF cap."

Does "increase the divided Voltage" mean increased VIH?

Regards,

Kosaka

HI Kosaka-san,

Regards,

Adrian Kam

Hi Adrian-san

We will change the circuit from step1 to step2.

But it still not clear so I would like to reconfirm the Not working reason with our original circuit step1.

Our clock mesurement result is meet the spec(VIH,VIL) If capacitor value is not infuruenced LSI, it should be working.

Which point do you highlight "not reduce the amplitude"?

Does it mean internal circuit in LSI? for out side capacitor value?

Regards,

Kosaka

I have additinal question for calcilation.

Original question1

We will change the circuit from step1 to step2.

But it still not clear so I would like to reconfirm the Not working reason with our original circuit step1.

Our clock mesurement result is meet the spec(VIH,VIL) If capacitor value is not infuruenced LSI, it should be working.

Which point do you highlight "not reduce the amplitude"?

Does it mean internal circuit in LSI? for out side capacitor value?

Additinal question2.

When we use CD1=27pF it is 236ohm. CD2=16pF it is 398ohm

Should we add the impedance of CD2?

This mean High Voltage =2.5V* 398/(236+398)=1.569V

Is this caluculation correct?

It is not include Phy own capacitor value.

Regards,

Kosaka

Hi Kosaka-san,

Regards,

Adrian Kam

Hi Adrian-san

Yes. I would like to reconfirm your before advice."The most likely reason is that the configuration in step 1 does not reduce the amplitude of the clock to below the absolute maximum rating."

I attached our clock signal image for step1 that is high voltage level is higher than 1.5V. But it did not work with 100metre cable.

Regards,

Kosaka

Hi Kosaka-san,

Yes, for step 1, you are using a 2.5V amplitude clock signal, and the configuration does not reduce the amplitude of the clock to below the maximum spec of Vosc (which is 1.9V).

If you are referring the the clock signal image previously attached, then the signal amplitude is higher than 1.5V but it also seems to be higher than 1.9V. Try to get the amplitude to 1.8V, which is what we recommend.

If you are referring to a new image, then I do not see it on this thread.

Regards,

Adrian Kam

Hi Adrian-san

(1) Thank you for reply But I am still not clear.

Max signal level of Step1 was 1.89V. 2.11v is Peak to Peak value that is from Low signal. But it could not connect with 100metre cable.

Is there other point?

(2)We will make new board that is following Data sheet(Step2) that conbination is 27pF+10pF.

Regards,

Kosaka

Hi Kosaka-san,

The Vosc value is peak-to-peak value. So the 2.11 peak-to-peak value in step 1 is too high.

I look forward to seeing the results. If you still have issues after making the capacitor changes and ensuring the clock signal has a peak-to-peak value of around 1.8V, let me know.

Regards,

Adrian Kam

Hi Adrian-san

We tested around 1.67V with step3 configuration that is reported before.

We stopped turuning with step1 and we will chnage the divided ciucuit to step2.

But we would like to know root case for step2 ciucuit.

When we test with step3 that is also 2.1V. It was working with 100metre cable. Absolute Maximum Ratings is 2.1V in the Data sheet.

So It seems there is other point. Is there Max load capacitor value spec viewing from LSI side?

Regards,

Kosaka

Hi Kosaka-san,

Let me ask my team about this, and I will respond by Friday at the latest.

Regards,

Adrian Kam

Hi Adrian-san

We have to respin soon. Make a new board. So I would like to clear the root cause.

May I have a information from your team ASAP.

Regards,

Kosaka

Hello Tadashi-san,

We are working internally to provide your recomended values. However it will take us one week to confirm.

Regards,

Geet

Hello Geet-san

My request is We would like to know the root casue with our original circuit(Step1) What was wrong?

We have to make a prodution Board ASAP.

So We wiil start to make a new board with step2(27pF+10pF) .

Regards,

Kosaka

Hello Geet-san

We would like to make clear.

Q1. What is root case for Step1 configuration?

I concerned that this configation increses the load capacitor for OSC side view.

Q2. For new board desgin with step2.

Does DP83867IR accept with 27pF+10pF conbination?

Hello Geet-san

Q3.When we make a recomend ciucuit(step2) with temporary,there is reflection.

Is there recommend cuitcuit?

Q4.We make a new circuit for new board. May TI review it? We already provided it to TI Japan

Regards,

Kosaka

Hello Tadashi-san,

I could not follow step 1 and step 2. Can you pleas re-write both steps to help answer.

Regards,

Geet

Hello Geet-san

Step1 is following

step2 is following but when we use 16pF. High level was low(around 1.5V). So we change to 10pF.

I attached signal image but this cuircuit has reflection.

Please share with Adrian san we were disscussing.

May we review new board circuit by TI?

Regards,

Kosaka

Hello Kosaka-san,

Thanks for the inputs.

For step 1:

1. The wave form is measured at which place ?

2. To isolate whether the reflections are due to the layout or capacitor divider, have you tried connecting external 1.8V clock source and check the reflections and link-up with 100 meter ?

Regards,

Geet

Hello Geet-san

A1.It is at LSI(DP83867)input pin

A2.Our cuicuit does not have 1.8V and Step2 is following Data sheet cuircuit.

Does TI recommend 1.8V? or X'tal?

Please answer for my other quetion too. Because we don't have a time.

And May TI review our new circuit and Could you accsess with TI Japan?

Regards,

Kosaka

A.2 : It is difficult to comment the reflection is due to mismatch of capacitor. That's why we want you to test with 1.8V Osc or XTAL to isolate the issue.

Regards,

Geet

Hello Geet-san

May I have a TI test result for reflection?

And we would like to clear the root cause for our original circuit soon.

Regards,

Kosaka

Hello Geet-san

We are designing new board now.

So Could TI provide recommended capacitor value?

Regards,

Kosaka