Part Number: SN65DP159

Hi

Cloud you help to check SN65DP159 schematic as below and any need to adjust

Thanks you

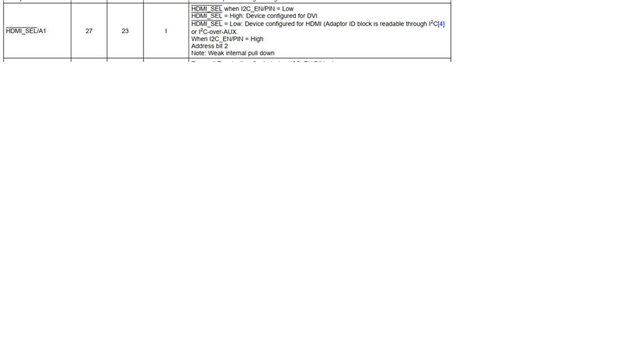

a. HDMI_SEL# High: Will I be unable to use I2C over AUX?

b. HDMI_SEL# Low: Does the DP-HDMI Adaptor ID have any effect? (DVI CONN at the end)