Hi team,

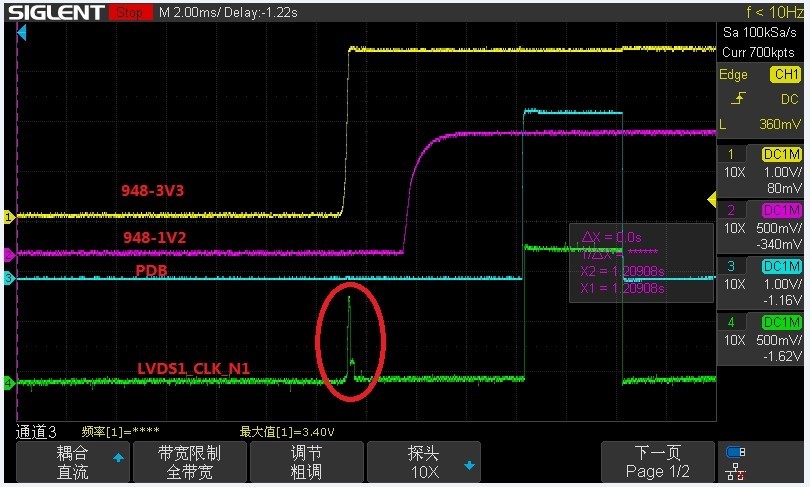

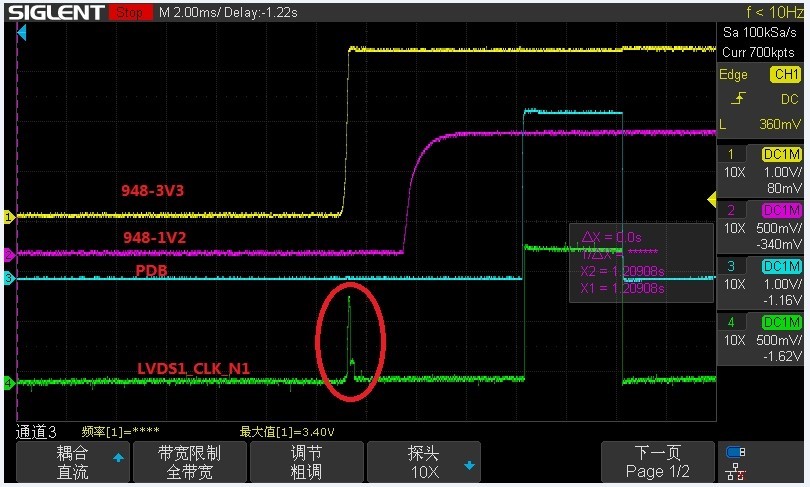

customer found when 948 VDD3.3V power up, the CLK have a pulse, see the below picture 1, The PDB is low.

search on E2E, I find some thread with the same issue that when 3.3V power on, 948 lock or GPIO have pulse, but didn't find the root cause and solution.

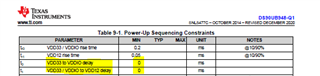

in additional, if 1.2V power on before 3.3V, the pulse can be reduce some, see the picture 2. but as 948 d/s, the 1.2V should not power before 3.3V.

so, we need your help is that how to reduce the pulse, at the same time meet 948 power sequence. what's your recommendation about delay time between 3.3V and 1.2V?

thank you.