Other Parts Discussed in Thread: TPS65987D

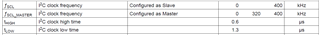

On the TPS65987D[Dx] spec. regarding I2C Master operation in Fast Mode there's this curious specification that the Typical fSCl_Master is 320 KHz.

It seems I2C master mode characteristics (such as clock frequency) are really configured by TI's FW rather than by the user as is the case in a typical microprocessor endowed with an I2C master controller - at least I haven't found a Clock Frequency setting in the Application Customization Tool. Does that means that TI programs at the factory some value for the master clock frequency which "typically" is 320KHz? Is that perhaps based on achieving minimal compliance of 1.3μs for tLow? tLow is typically a challenge to meet as it's greater than a 400KHz half-cycle of 1.25μs, generally requiring a slight reduction of below 400KHz to achieve compliance.

Furthermore, albeit such Master I2C has 3.3V Pull-Ups (powered by LDO_3V3), does this e2e.ti.com/.../tps65987d-tps65987d-i2c-input-threshold-for-ldo_1v8-and-ldo_3v3 article imply that one shall use the 1.8V VIH & VIL I2C levels to characterize I2C inputs into such TPS6597D[Dx] I2C inputs - particularly the SDa line?

Reason I ask these questions is that I for example see on my board SCl clock frequency of 335KHz (which conceivably should be able to yield a tLow of around 1.49μs) with tLow being about 1.33μs (very close to the 1.3μs I2C limit). I thus wonder if there is some tolerance (particularly across temperature) where some specimens could actually have tLow below the required 1.3μs. Furthermore, we have N-FETs based 3.3V to 1.8V translators (along the lines of www.nxp.com/.../AN10441.pdf), where those translators tend to reduce a bit the low time so even though the TPS65987DDx may not violate tLow, a slave connected to it may be receiving a clock that is on violation.

Is it at all possible for a user to configure the clock frequency of a TPS65987D[Dx] I2C Master controller???

Thanks so very much,

Georg A. Mussenden