Hi Team,

I have a question about power sequence of DP83869HM.

My customer is evaluating DP83869HM and they faced below problem.

They are looking for the root cause and they have concern about power sequence.

[Problem]

DP83869HM doesn't establish the link with etherhub.

when read the register value, All register value are FFFF.

after HW reset, return to normal behavior(establish the link).

[Concern]

t1_VDDIO(supply ramp time) is close to 0.5ms_min.

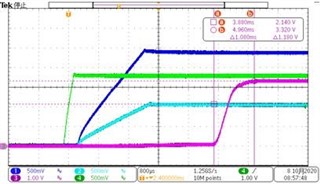

below pink is VDDIO and supply ramp time is 1.08ms but depending on % of rise time(e.g. 20% - 80%), it might be less than 0.5ms.

[Question]

when t1_VDDIO is less than 0.5ms_min, does Phy duplicate above problem?

If yes, are there any sweet time that can easily duplicate above problem?

Regards,

Kai