Part Number: DP83867E

Hi,

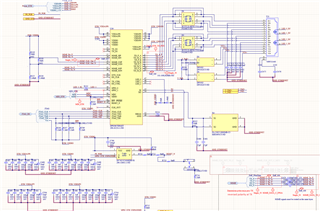

We have DP83867E communicating with ZU4CG in our custom board by SGMII (4 wire), clock 125MHz for FPGA comes form external distributor. We read registers by mdio interface, most of them looks correct, but some (0x6E, 0x6F) doesn't, even if we reset DP83867E by software or hardware.

Our strap configuration:

RX_CTRL - MODE3

LED_0 - MODE2

ADDRESS set - 0xA

Registers:

ZynqMP> mii read 0xa 0x0

1140

ZynqMP> mii read 0xa 0x1

796D

ZynqMP> mii read 0xa 0x2

2000

ZynqMP> mii read 0xa 0x3

A231

ZynqMP> mii read 0xa 0x4

01E1

ZynqMP> mii read 0xa 0x5

C1E1

ZynqMP> mii read 0xa 0x6

006F

ZynqMP> mii read 0xa 0x7

2001

ZynqMP> mii read 0xa 0x8

6801

ZynqMP> mii read 0xa 0x9

0300

ZynqMP> mii read 0xa 0xa

3C00

ZynqMP> mii read 0xa 0xb

0000

ZynqMP> mii read 0xa 0xc

0000

ZynqMP> mii read 0xa 0xd

401F

ZynqMP> mii read 0xa 0xe

0000

ZynqMP> mii read 0xa 0xf

3000

ZynqMP> mii read 0xa 0x10

5840

ZynqMP> mii read 0xa 0x11

BE02

ZynqMP> mii read 0xa 0x12

0000

ZynqMP> mii read 0xa 0x13

1C42

ZynqMP> mii read 0xa 0x14

29C7

ZynqMP> mii read 0xa 0x15

0000

ZynqMP> mii read 0xa 0x16

0000

ZynqMP> mii read 0xa 0x17

0040

ZynqMP> mii read 0xa 0x18

6150

ZynqMP> mii read 0xa 0x19

4444

ZynqMP> mii read 0xa 0x1a

0002

ZynqMP> mii read 0xa 0x1b

0000

ZynqMP> mii read 0xa 0x1c

0000

ZynqMP> mii read 0xa 0x1d

0000

ZynqMP> mii read 0xa 0x1e

0002

ZynqMP> mii read 0xa 0x1f

0000

ZynqMP> mii read 0xa 0x20

FFFF

ZynqMP> mii read 0xa 0x6e

FFFF

ZynqMP> mii read 0xa 0x6f

FFFF

What can cause the problem with these registers?