Part Number: DS90UB947-Q1

Hi team,

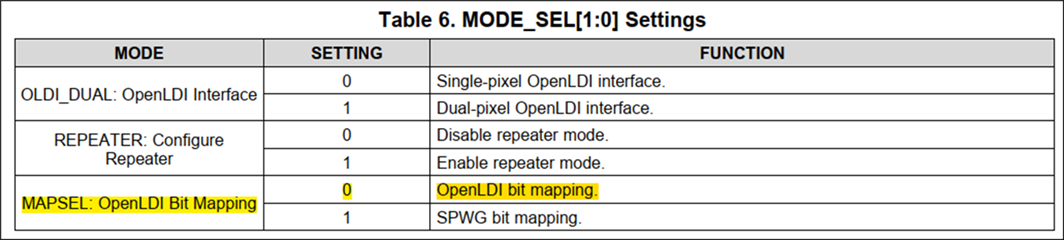

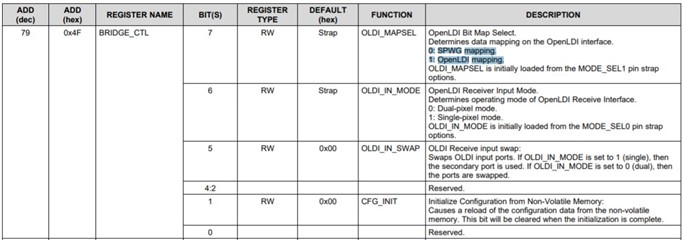

Since for 947, MAPSEL=1 is OpenLDI bit mapping, can you check if we will correct the error in datasheet shown below? If yes, do you have timeline for the plan?

Thanks.

Johnny

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DS90UB947-Q1

Hi team,

Since for 947, MAPSEL=1 is OpenLDI bit mapping, can you check if we will correct the error in datasheet shown below? If yes, do you have timeline for the plan?

Thanks.

Johnny

Hello Johnny,

why do you believe this is wrong and should be corrected?

Having 1 or 0 in the register does not mean you should have the same value in the MODE_SEL table!!

Hi Jaradat,

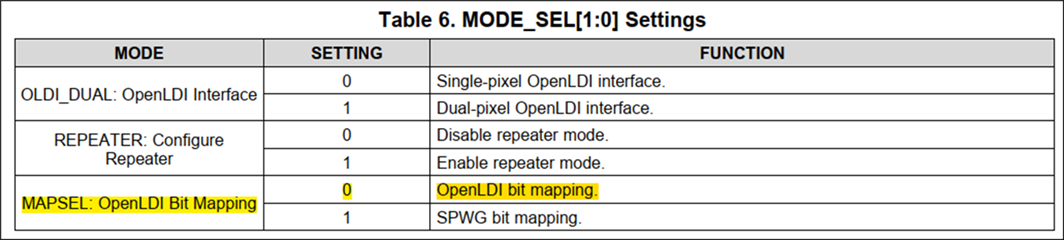

Please correct me if I am wrong. In below FAQ, and in datasheet BRIDGE_CTL register, "1" means OpenLDI mapping.

Hello Johnny,

The register values are correct. 0: SPWG and 1: oLDI. Similarly 0: Dual-pixel and 1: single pixel.

I know this is a bit confusing, but this does not need to match with the MODE_SEL table. The table values are configured via resistors. But once you chose the correct configuration using resistors, this will be reflected with the correct value in register 0x4F.

Hi Hamzeh,

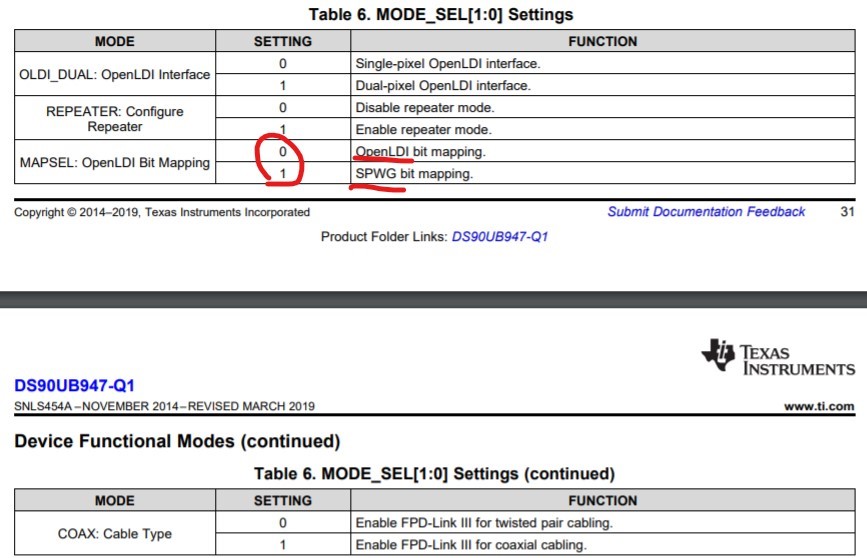

Thanks for reply, but how to understand the setting "0" and "1" in MODE_SEL settings table? Just need to align "0" and "1" in following Configuration Select table? Not the direct mapping to register bit "0" and "1"?

Hello Johnny,

In the MODE_SEL1 table, in the column MAPSEL, if you chose 0 then you are selecting oLDI mapping, but if you chose 1 then you are selecting SPWG.

For our application, when we choose 0,the TFT display abnormal,and choose the TFT display normal.

Also i have searched the related question from E2E, feedback the MAPsel was error in datasheet, Hyperlink as below:

Hello Johnny,

thanks for your feedback. Please let me double check this with the team and come back to you.

Hello Johny,

Please follow the answer provided in this ticket. It is the correct answer.