Hi Team,

Customer designed TMDS181 and raised two questions. Would you please help?

1. About the termination of the setting in I2C mode, this register does not seem to be a fixed state. Would you please explain about this register usage?

2. Could you explain who writes 1 to the TMDS_CLOCK_RATIO_STATUS bit?

As datasheet the page 24, upon return to normal active operation from reasserted OE or reasserted HPD, the TMDS181 requires the source to write a 1 to the TMDS_CLOCK_RATIO_STATUS bit for the TMDS181 to resume 1/40th clock mode. The TMDS181 does not reset this bit based upon a DDC read transaction.

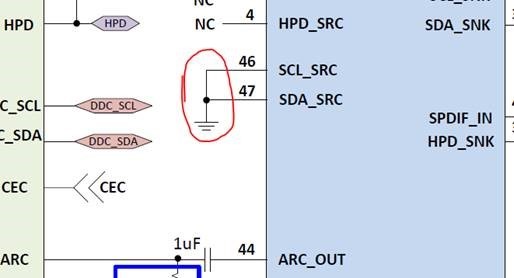

3. Can customer let the two pins of SCL_SRC and SDA_SRC be floating?

BR,

SHH