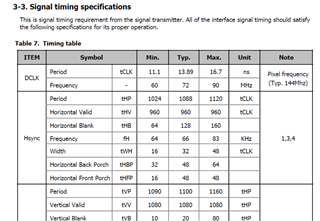

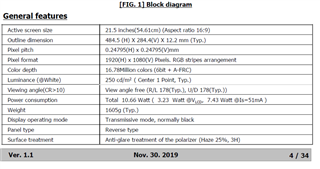

Below is the specs of display that I am using with SN65DSI84ZXHR. I am using 65MHZ crystal. Is that okay to go with or should i go for higher or lower value?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.