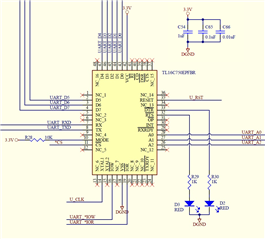

Part Number: TL16C750E

I am are having difficulty getting the TL16C750E UART to read data correctly.

The problem looks to be in the internal buffer.

Background:

Test code is initializing the device to operate in a non FIFO, polled mode, with the parity bit code controlled for 9 bit data operation.

If the following initialization sequence is incorrect to achieve that, please let me know how to correct it:

Reset (50us high pulse)

LCR <-- 0xBF

EFR < -- 0x10

LCR < -- 0x83

DLH < -- V1 --+

DLL < -- V2 | -- >1 M BAUD

DLF < -- V3 --+

LCR < -- 0xBF

EFR < -- 0x00

LCR < -- 0x03

IER < -- 0x00

FCR < -- 0x00

A separate board sends incrementing (by 1) byte values ( 9 bit data) at a slow rate (so there is no problem with data over runs), and its code is always started first.

After the above initialization, the TL16C750E test code sends a value to that board to trigger it to start sending its slow data and then polls bit 0 of the LSR, looking for a new received byte:

Read LSR until THR empty is true..

MCR < -- 0x02 (/DTS and /RTS outputs drive LEDs)

LCR < -- 0x2B ( 9 bit data via code controlled parity bit)

THR < -- data to trigger response

count=0 log detects of new bytes received

forever loop:

Read LSR until "data in receiver" bit =1

if true

increment count

Read RHR for the data byte

if the data >0

log the data

log the value of count

endif

endif

end of forever loop

What I see in the log results are:

1. The true data does not start until after reading 128 bytes. Note: LSR "data in receiver" bit correctly updates each time.

The first 64 are always 0x00, and the next 64 are incorrect, with the first byte of that second 64 close, such as 0xC5,when the true data is 0x05, with increments from 0xC5 on subsequent bytes.

2. If the starting value from the other board is changed, that 128th read value is not correct until:

a. the TL16C750E test code is run twice

b. the TL16C750E board is power cycled.

The intent is for the UART to operate in a non-FIFO, polling mode, so according to the data sheet : "If the FIFO is disabled, location 0 of the FIFO is used to store the characters" (section 9.5.2)

But the storage and read internal pointers still seem to be using the entire 128 byte FIFO, vs only using location 0 for both the storage and reading from.

Thanks in advance for you help.