Part Number: SN65HVD72

Hi Team,

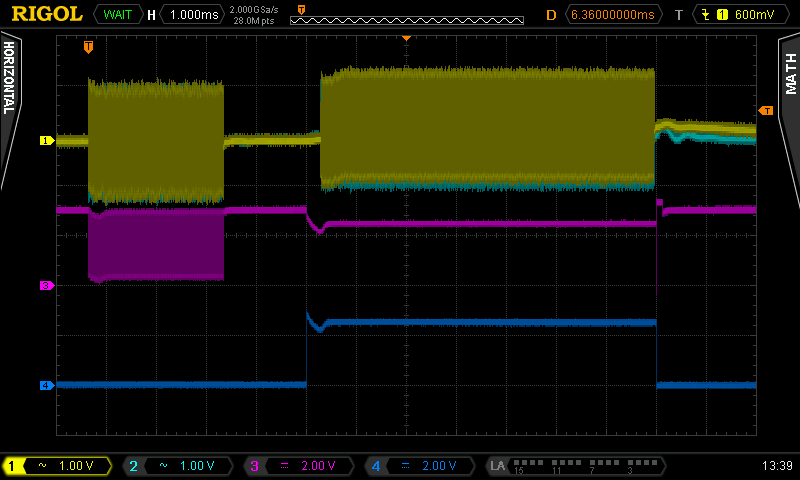

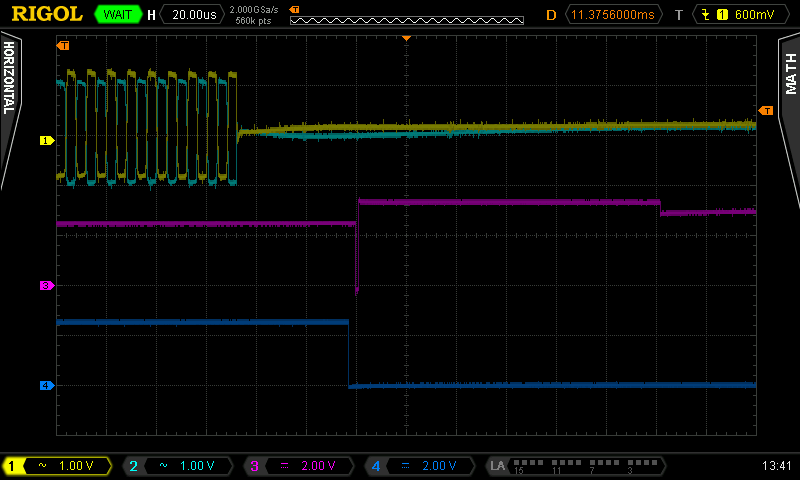

I use SN65HVD72 on one RS485 bus.

On one side of the bus (on the device)

when changing the nRE pin (from HIGHT to LOW and from LOW to HIGHT),

the Rx pin changes (LOW: duration 500ns)

It should be in a HIGHT state!

What's the problem?

Thanks and best regards,

Stjepan