Part Number: DP83867IR

HI,

I'm using the DP83867IRPAPR Ethernet PHY for ethernet packet transmission ( For RGMII transmission).

Need to configure the chip for frame transmission but when i try to read the chip identifier register, the chip is not responding properly. I'm getting the default value as 0xffff.

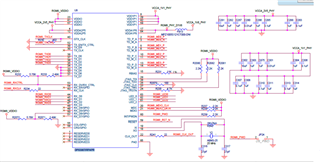

Below I attached the schematic of PHY with FPGA, there is no strap configuration for R0 and R2 so the PHY address is 0x00.

RSD0 and RXD2 are directly connected to FPGA IO.

I'm trying to read the address 0x0002, which should return the value 0x2000.

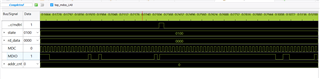

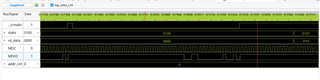

Below is the driving signal of MDC and MDO.

1) Address write

2) Read at 0x0002 address

I'm using clause - 45 type protocol to access the extended registers.

Frequency tried - 2.5 Mhz, 5 Mhz, 10 Mhz.

Kindly, Help me to resolve this reading problem.