Hi Experts,

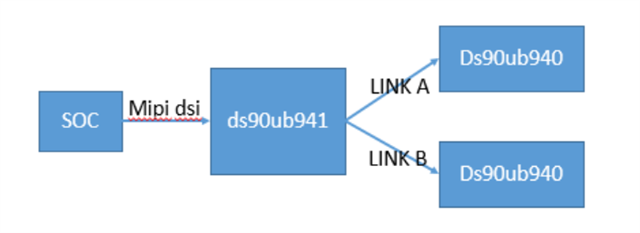

Our company is using DS90UB941 as display serializer. The connection is as below:

Now, it can display with single Link A or Link B. However, when I try to configure them to display together, replicate or splitter mode, some problems are encountered. Could you help to solve them?

Q1: ds90ub941 works at replicate mode

SOC outputs 720p60 MIPI DSI. After mipi dsi is valid, I need to set register 0x5B to 0x1(force single link mode), then reset it to 0x0(auto link mode). Otherwise, both ds90ub940 cannot display images. But both ds90ub940s' lock and pass are active. If I set 0x5B to 0x1 and reset 0x5B to 0x0, both ds90ub940s can display successfully.

Could you help to provide a simple register setting for replicate mode or modify my setting?

The following registers are ds90ub941's configuration.

/* disable dsi */ ds90ub941_write_reg(ds90ub941, addr, 0x01, 0x08); /* Initialize internal DSI clock settings */ ds90ub941_write_reg(ds90ub941, addr, 0x40, 0x10); ds90ub941_write_reg(ds90ub941, addr, 0x41, 0x86); ds90ub941_write_reg(ds90ub941, addr, 0x42, 0x0A); ds90ub941_write_reg(ds90ub941, addr, 0x41, 0x94); ds90ub941_write_reg(ds90ub941, addr, 0x42, 0x0A); /* enable continuous clock mode */ ds90ub941_write_reg(ds90ub941, addr, 0x4F, 0x80); /* enable dsi reference clock mode */ ds90ub941_write_reg(ds90ub941, addr, 0x56, 0x00); /* select DSI port0 */ ds90ub941_write_reg(ds90ub941, addr, 0x40, 0x04); ds90ub941_write_reg(ds90ub941, addr, 0x41, 0x05); ds90ub941_write_reg(ds90ub941, addr, 0x42, 0x12); /* Enable DSI */ ds90ub941_write_reg(ds90ub941, addr, 0x01, 0x00);

Q2: ds90ub941 works at splitter mode

Another request is that we want to display two different videos on ds90ub941s.

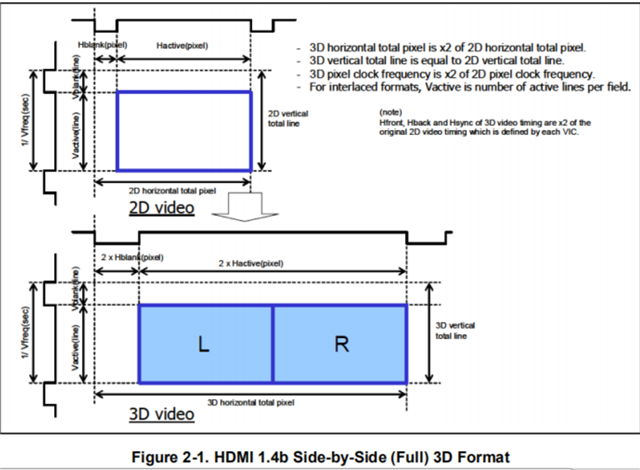

Figure 2-1 in doc SNLA308A says that 3D horizontal total pixel is x2 of 2D horizontal total pixel. If my 2D image horizontal total pixel is 1650(hbp 74, hsync 85, hfp 211, h_act 1280), the 3D horizontal total pixel will be 1650x2=3300(hbp 148, hsync 170, hfp 422, h_act 2560). And vertical size doesn't change. Is it right?

Looking forward to your reply. Thank you very much.

Best regards,

Justin Ding