Other Parts Discussed in Thread: DP83869,

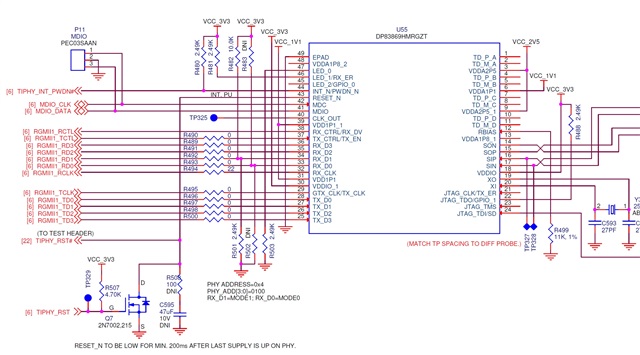

We are using a DP83869 between an AM335x and a 1G SFP. On the SFP side, the link is coming up. However the SGMII interface to the AM335x is not working.

One thing I notice is that the GEN_STATUS1 register in the DP83869 is 0, indicating "local receiver not okay" and "remote receiver not okay".

First question: What would make them "not okay"?

RGMII_CTRL is 0x00d0, indicating that the transmit and receive clocks are shifted with respect to the data. I have tried a number of values for DLL_TX_DELAY_CTRL_SL and DLL_RX_DELAY_CTRL_SL in ANA_RGMII_DLL_CTRL.

Second question: What are the delay values DLL_TX_DELAY_CTRL_SL and DLL_RX_DELAY_CTRL_SL a measurement of (between what and what)? The description indicates that they affect CLK_90, but CLK_90 does not appear elsewhere in the datasheet.

In case it has an effect: The 1G SFP wire-side is an RJ45 copper connection going to a switch. CFG_OPMODE is 1. Although the switch supports 1G, this link is being negotiated to 100/half. This causes the AM335x side to set the Tx RGMII clock to 25MHz, while the RX clock from the PHY is at 125 MHz.

Thanks,

Steve