Part Number: DP83869HM

Hi team,

Do you have any test data for latch up, especially for MDI-pins?

Regards,

Noriyuki Takahashi

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DP83869HM

Hi team,

Do you have any test data for latch up, especially for MDI-pins?

Regards,

Noriyuki Takahashi

Hi Noriyuki,

Can you clarify what you mean by latch up? Are you referring to timing requirements? Is this with regard to failure after an ESD event?

Thanks,

Lucas

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).

Lucas,

Sorry for late reply.

This is for failure after an ESD event.

Regards,

Noriyuki Takahashi

Hi Noriyuki,

The PHY is tested based on the IEC 61000-4-2 standard. You can refer to section 8.2 of the datasheet for information on ESD ratings.

Thanks,

Lucas

Hi Lucas

Latch-up test is different with ESD test as below app note. Could you confirm again whether TI has the data for latch-up test? Customer wants the date for the latch-up test.

https://www.tij.co.jp/jp/lit/an/slya014a/slya014a.pdf

Regards,

Noriyuki Takahashi

Hi Noriyuki,

Which standard and test are you asking for? Under what condition do you want latch-up? Latch-up test is part of our ESD testing, which can be found in section 8.2 of the datasheet.

Thanks,

Lucas

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).

Hi Noriyuki,

As we have not heard back in a while, we will be closing this thread. If you still require additional technical support, please open a new thread with a link to this one.

Thank you,

Nikhil

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).

Sorry for late response.

Are there any date about JESD78 that is the standard of latch-up testing?

Regards,

Noriyuki Takahashi

Hi Noriyuki,

I am looking into this test standard and will be able to provide additional feedback by tomorrow.

Thank you,

Nikhil

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).

Hi Noriyuki,

We follow the TI recommended ESD standards for Ethernet PHY devices as noted by Section 8.2 in the datasheet. We do not perform the JESD78 testing.

Thank you,

Nikhil

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).

Nikhil,

Looking at Quality, reliability & packaging information of the device, it seems that DP83869HM could pass JESD78. Is this true? Could you confirm this?

If this is true, could you confirm which pins are tested for JESD78?

Regards,

Noriyuki Takahashi

Hi Noriyuki,

Thank you for the eply.

As mentioned above, We do not perform the JESD78 testing.

R

Regards,

Sreenivasa

Sreenivasa,

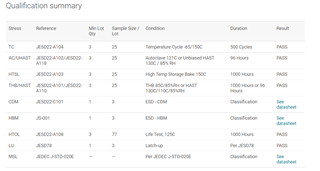

You can see one DP83869HM passed the latch up test as the attached below. You can see this from the link as below. How should I understand this?

https://www.ti.com/quality-reliability-packaging-download/report?opn=DP83869HMRGZT

Regards,

Noriyuki Takahashi

Hi Noriyuki,

Thank you for the table. This could be an internal qualification test but not specified in the datasheet as seen in the table you have sent.

Regards,

Sreenivasa

Sreenivasa,

Could you confirm which pins are tested for JESD78?

Regards,

Noriyuki Takahashi

I mean, do you have supplemental information for the test?

Regards,

Noriyuki Takahashi

Hi Noriyuki,

We do not have the data that that could be reviewed and provided. Could you please provide some additional inputs on the use case ?

Regards,

Sreenivasa

Hello Noriyuki,

Please see the inputs i have received.

We are testing all pins under LU test.

We are following the JEDEC standard as highlighted in the screen shot you provided ( above) and I would refer the customer to the spec for additional clarification if needed.

Regards,

Sreenivasa