dear,expert:

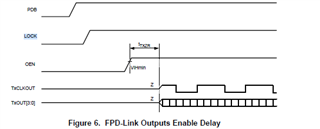

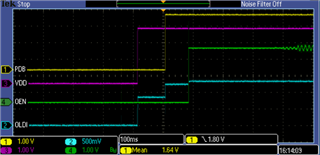

accodrding to 928 datasheet ,when VDD33 and VDDIO power up,pdb and oen power up,oldi(TxOUT(3:0),TxCLKOUT) output from 0V to normally,but in fact test ,when VDD33 and VDDIO power up ,the PDB and OEN not power up, this time test the OLDI output above 1V DC level, when PDB power up,the OLDI output 1.2V DC level;

1.so I want to know whether this phenomenon is normal;

2.Can I set the OLDI output to 0V by set the registers ?