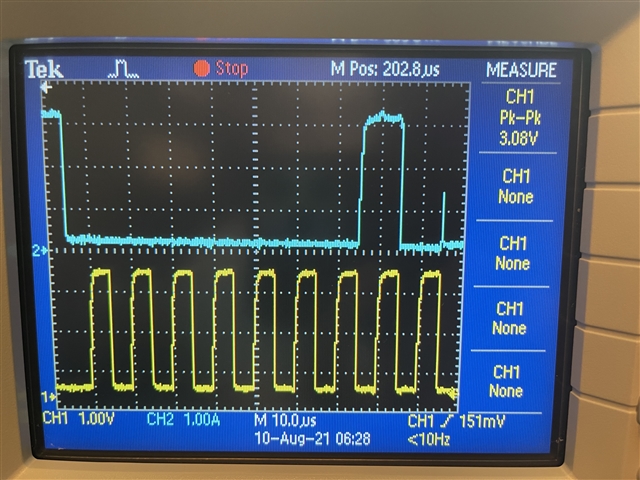

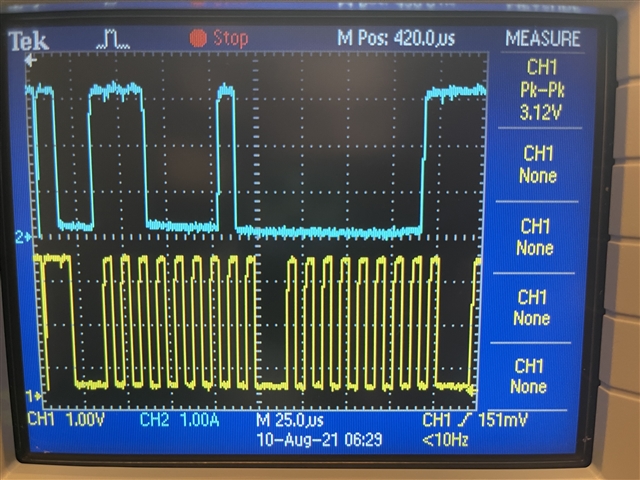

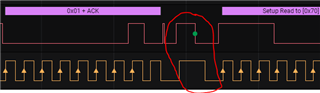

I have the mux fully operational and have been using it for weeks but am just now getting around to writing the actual interface. I want to read the status out of the mux for interrupts and for confirming buses are enabled. Even though I'm successfully enabling bus 0 via the write command, reading it back always gives 0 for bit 0. I thought perhaps reading back the register too quickly after a write was the issue so I have a second read and the value hasn't changed.

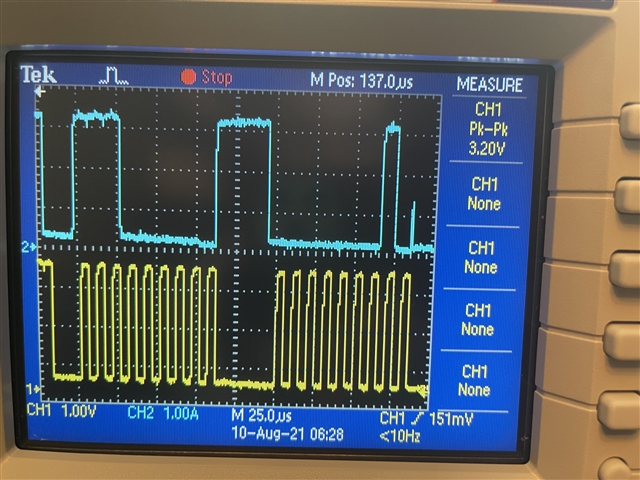

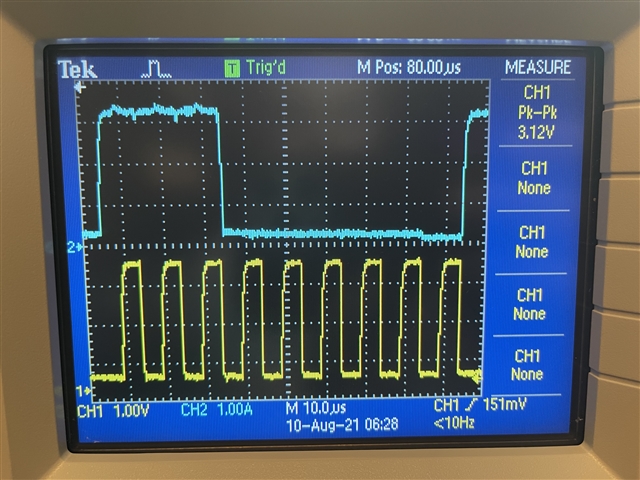

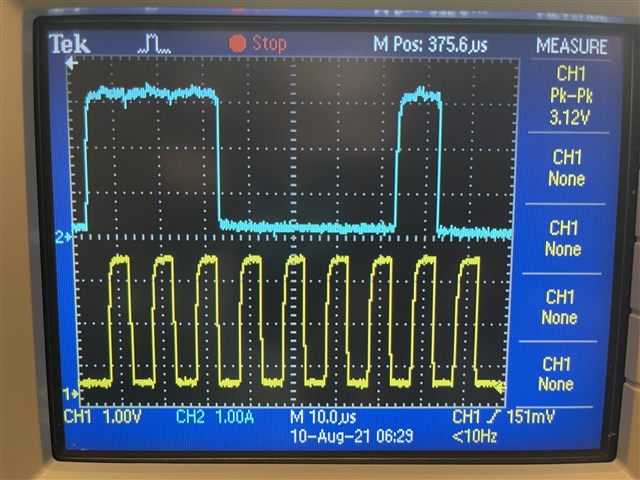

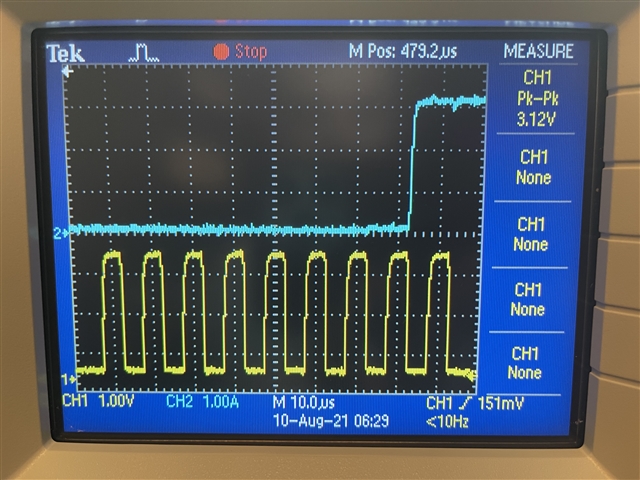

As you can see in the capture, the buses become active once the command is received. But Even sending 0x09 gives back 0x08 when reading the register.

And it isn't processor side, the timing is clean. I've been using bus 0 for weeks now to read various other devices.