Hello Expert,

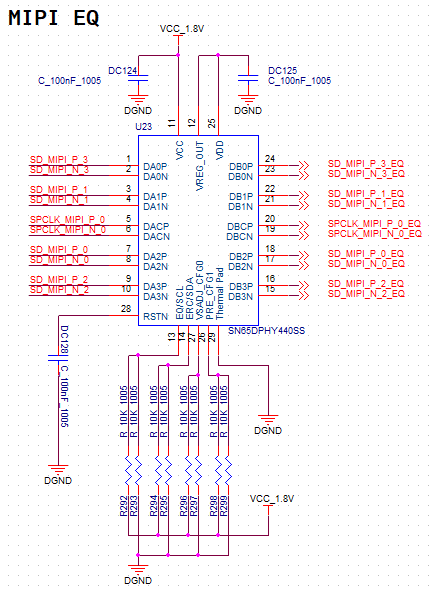

Our customer is routing pcb pattern w/ this part.

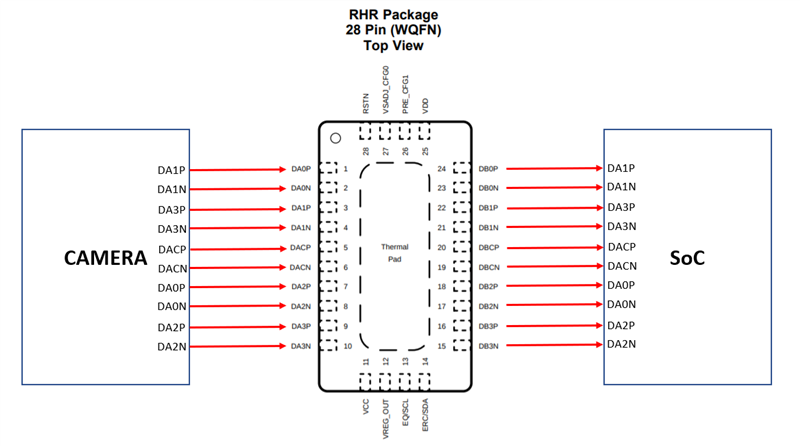

They are facing to the issue of crossing MIPI signals.

I think that this device has not a channel swap function.

So I'd like to get confirm whether it is ok or not like below diagram.

I think that is ok.

Could you please give me your feedback?

Best regards,

Michael