Other Parts Discussed in Thread: USB-2-MDIO

Good Afternoon,

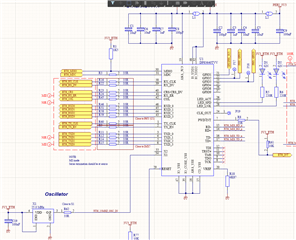

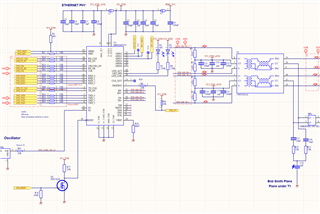

I currently have a custom board with an iMX7d (On an EA iMX7d uCOM SOM) connected to a DP8360 PHY via MII and I don't seem to be able to get comms working properly over the MII interface. The PHY is discovered and configured correctly over the MDIO bus and I can see sent TX packets in wireshark from UBOOT. Hoping I've missed something in the device tree,

Current Device Tree,

&fec1 { pinctrl-names = "default"; pinctrl-0 = <&pinctrl_enet1>;

clocks = <&clks IMX7D_ENET_AXI_ROOT_CLK>, <&clks IMX7D_ENET_AXI_ROOT_CLK>, <&clks IMX7D_ENET1_TIME_ROOT_CLK>, <&clks IMX7D_PLL_ENET_MAIN_25M_CLK>; clock-names = "ipg", "ahb", "ptp", "enet_clk_ref";

assigned-clocks = <&clks IMX7D_ENET1_TIME_ROOT_SRC>, <&clks IMX7D_ENET1_TIME_ROOT_CLK>; assigned-clock-parents = <&clks IMX7D_PLL_ENET_MAIN_25M_CLK>; assigned-clock-rates = <0>, <100000000>; phy-mode = "mii"; phy-handle = <ðphy0>; fsl,magic-packet; status = "okay";

mdio { #address-cells = <1>; #size-cells = <0>;

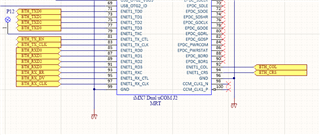

ethphy0: ethernet-phy@0 { compatible = "ethernet-phy-ieee802.3-c22"; reg = <1>; }; };};pinctrl_enet1: enet1grp { fsl,pins = <

MX7D_PAD_ENET1_COL__ENET1_COL 0x1 MX7D_PAD_ENET1_CRS__ENET1_CRS 0x1

MX7D_PAD_GPIO1_IO11__ENET1_MDC 0x3 MX7D_PAD_GPIO1_IO10__ENET1_MDIO 0x3

MX7D_PAD_ENET1_RX_CLK__ENET1_RX_CLK 0x1 MX7D_PAD_ENET1_RGMII_RXC__ENET1_RX_ER 0x1

MX7D_PAD_ENET1_TX_CLK__CCM_ENET_REF_CLK1 0x1

MX7D_PAD_ENET1_RGMII_RD0__ENET1_RGMII_RD0 0x1 MX7D_PAD_ENET1_RGMII_RD1__ENET1_RGMII_RD1 0x1 MX7D_PAD_ENET1_RGMII_RD2__ENET1_RGMII_RD2 0x1 MX7D_PAD_ENET1_RGMII_RD3__ENET1_RGMII_RD3 0x1

MX7D_PAD_ENET1_RGMII_RX_CTL__ENET1_RGMII_RX_CTL 0x1 MX7D_PAD_ENET1_RGMII_RXC__ENET1_RGMII_RXC 0x1

MX7D_PAD_ENET1_RGMII_TD0__ENET1_RGMII_TD0 0x3 MX7D_PAD_ENET1_RGMII_TD1__ENET1_RGMII_TD1 0x3 MX7D_PAD_ENET1_RGMII_TD2__ENET1_RGMII_TD2 0x3 MX7D_PAD_ENET1_RGMII_TD3__ENET1_RGMII_TD3 0x3 >; };