Part Number: DS90UB962-Q1

Dear expert,

My system is Camera-935-962-ISP. Only one Camera attached during test. If power down camera and then power up camera, ISP cannot recognize CSI signal from 962. However, if there is 962 CSI reset between camera power down& power up, ISP can recognize CSI signal from 962.

NOTE: "962 CSI reset" mean: set register 0x33 to 0 to disable and then set to 0x3 to enable CSI

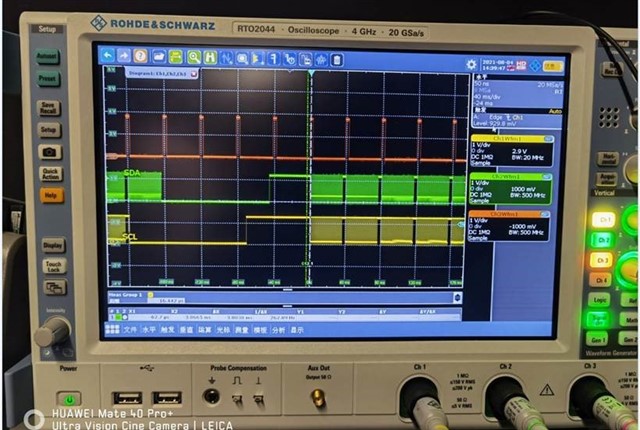

Below is captured CSI signal. Green is CSI data 0 signal from camera to 935. Yellow is CSI data 0 signal from 962 to ISP. Orange is frame sync which you can ignore.

I found during camera power down, CSI data 0 of 962 are hold to high (other CSI data and clock are similar). With CSI disable, CSI data jump to low, then jump to high when enable CSI. What's the purpose for this logic? Anything else is done during CSI disable &then enable?

ISP side is also checking the problem. However, need your guidance to give us some hint.

I also attached register setting below.

Great thanks

NO CSI reset:

With CSI reset:

962 reg 0x0, val 0x60 962 reg 0x1, val 0x0 962 reg 0x2, val 0x1e 962 reg 0x3, val 0x40 962 reg 0x4, val 0xd0 962 reg 0x5, val 0x1 962 reg 0x6, val 0x0 962 reg 0x7, val 0xfe 962 reg 0x8, val 0x1c 962 reg 0x9, val 0x10 962 reg 0xa, val 0x7a 962 reg 0xb, val 0x7a 962 reg 0xc, val 0xf 962 reg 0xd, val 0x9 962 reg 0xe, val 0x0 962 reg 0xf, val 0x0 962 reg 0x10, val 0x91 962 reg 0x11, val 0x0 962 reg 0x12, val 0x0 962 reg 0x13, val 0x0 962 reg 0x14, val 0x0 962 reg 0x15, val 0x0 962 reg 0x16, val 0x0 962 reg 0x17, val 0x0 962 reg 0x18, val 0x11 962 reg 0x19, val 0x1a 962 reg 0x1a, val 0xa 962 reg 0x1b, val 0xea 962 reg 0x1c, val 0x5a 962 reg 0x1d, val 0x0 962 reg 0x1e, val 0x4 962 reg 0x1f, val 0x0 962 reg 0x20, val 0xf0 962 reg 0x21, val 0x3 962 reg 0x22, val 0x0 962 reg 0x23, val 0x0 962 reg 0x24, val 0x0 962 reg 0x25, val 0x0 962 reg 0x26, val 0x0 962 reg 0x27, val 0x0 962 reg 0x28, val 0x0 962 reg 0x29, val 0x0 962 reg 0x2a, val 0x0 962 reg 0x2b, val 0x0 962 reg 0x2c, val 0x0 962 reg 0x2d, val 0x0 962 reg 0x2e, val 0x0 962 reg 0x2f, val 0x0 962 reg 0x30, val 0x0 962 reg 0x31, val 0x0 962 reg 0x32, val 0x1 962 reg 0x33, val 0x3 962 reg 0x34, val 0x0 962 reg 0x35, val 0x0 962 reg 0x36, val 0x0 962 reg 0x37, val 0x0 962 reg 0x38, val 0x0 962 reg 0x39, val 0x0 962 reg 0x3a, val 0x0 962 reg 0x3b, val 0x0 962 reg 0x3c, val 0x0 962 reg 0x3d, val 0x0 962 reg 0x3e, val 0x0 962 reg 0x3f, val 0x0 962 reg 0x40, val 0x0 962 reg 0x41, val 0xa9 962 reg 0x42, val 0x71 962 reg 0x43, val 0x1 962 reg 0x44, val 0x0 962 reg 0x45, val 0x0 962 reg 0x46, val 0x20 962 reg 0x47, val 0x0 962 reg 0x48, val 0x0 962 reg 0x49, val 0x0 962 reg 0x4a, val 0x0 962 reg 0x4b, val 0x12 962 reg 0x4c, val 0x12 962 reg 0x4d, val 0x43 962 reg 0x4e, val 0x4 962 reg 0x4f, val 0x64 962 reg 0x50, val 0x0 962 reg 0x51, val 0x0 962 reg 0x52, val 0x0 962 reg 0x53, val 0x2 962 reg 0x54, val 0x0 962 reg 0x55, val 0x0 962 reg 0x56, val 0x0 962 reg 0x57, val 0x0 962 reg 0x58, val 0x5e 962 reg 0x59, val 0x0 962 reg 0x5a, val 0x0 962 reg 0x5b, val 0x30 962 reg 0x5c, val 0x2a 962 reg 0x5d, val 0x38 962 reg 0x5e, val 0xa0 962 reg 0x5f, val 0x0 962 reg 0x60, val 0x0 962 reg 0x61, val 0x0 962 reg 0x62, val 0x0 962 reg 0x63, val 0x0 962 reg 0x64, val 0x0 962 reg 0x65, val 0x5a 962 reg 0x66, val 0xa2 962 reg 0x67, val 0x0 962 reg 0x68, val 0x0 962 reg 0x69, val 0x0 962 reg 0x6a, val 0x0 962 reg 0x6b, val 0x0 962 reg 0x6c, val 0x0 962 reg 0x6d, val 0x7c 962 reg 0x6e, val 0xa8 962 reg 0x6f, val 0x88 962 reg 0x70, val 0x6b 962 reg 0x71, val 0x6c 962 reg 0x72, val 0xe5 962 reg 0x73, val 0x0 962 reg 0x74, val 0x0 962 reg 0x75, val 0x0 962 reg 0x76, val 0x0 962 reg 0x77, val 0xc5 962 reg 0x78, val 0x1 962 reg 0x79, val 0x1 962 reg 0x7a, val 0x0 962 reg 0x7b, val 0x0 962 reg 0x7c, val 0x20 962 reg 0x7d, val 0x0 962 reg 0x7e, val 0x0 962 reg 0x7f, val 0x0 962 reg 0x80, val 0x0 962 reg 0x81, val 0x0 962 reg 0x82, val 0x0 962 reg 0x83, val 0x0 962 reg 0x84, val 0x0 962 reg 0x85, val 0x0 962 reg 0x86, val 0x0 962 reg 0x87, val 0x0 962 reg 0x88, val 0x0 962 reg 0x89, val 0x0 962 reg 0x8a, val 0x0 962 reg 0x8b, val 0x0 962 reg 0x8c, val 0x0 962 reg 0x8d, val 0x0 962 reg 0x8e, val 0x0 962 reg 0x8f, val 0x0 962 reg 0x90, val 0x0 962 reg 0x91, val 0x0 962 reg 0x92, val 0x0 962 reg 0x93, val 0x0 962 reg 0x94, val 0x0 962 reg 0x95, val 0x0 962 reg 0x96, val 0x0 962 reg 0x97, val 0x0 962 reg 0x98, val 0x0 962 reg 0x99, val 0x0 962 reg 0x9a, val 0x0 962 reg 0x9b, val 0x0 962 reg 0x9c, val 0x0 962 reg 0x9d, val 0x0 962 reg 0x9e, val 0x0 962 reg 0x9f, val 0x0 962 reg 0xa0, val 0x0 962 reg 0xa1, val 0x0 962 reg 0xa2, val 0x0 962 reg 0xa3, val 0x0 962 reg 0xa4, val 0x0 962 reg 0xa5, val 0x1a 962 reg 0xa6, val 0x0 962 reg 0xa7, val 0x0 962 reg 0xa8, val 0x0 962 reg 0xa9, val 0x0 962 reg 0xaa, val 0x0 962 reg 0xab, val 0x0 962 reg 0xac, val 0x0 962 reg 0xad, val 0x0 962 reg 0xae, val 0x0 962 reg 0xaf, val 0x0 962 reg 0xb0, val 0x1c 962 reg 0xb1, val 0x3a 962 reg 0xb2, val 0x14 962 reg 0xb3, val 0x8 962 reg 0xb4, val 0x25 962 reg 0xb5, val 0x0 962 reg 0xb6, val 0x18 962 reg 0xb7, val 0x0 962 reg 0xb8, val 0x88 962 reg 0xb9, val 0x33 962 reg 0xba, val 0x83 962 reg 0xbb, val 0x74 962 reg 0xbc, val 0x80 962 reg 0xbd, val 0x0 962 reg 0xbe, val 0x0 962 reg 0xbf, val 0x0 962 reg 0xc0, val 0x0 962 reg 0xc1, val 0x0 962 reg 0xc2, val 0x0 962 reg 0xc3, val 0x0 962 reg 0xc4, val 0x0 962 reg 0xc5, val 0x0 962 reg 0xc6, val 0x0 962 reg 0xc7, val 0x0 962 reg 0xc8, val 0x0 962 reg 0xc9, val 0x0 962 reg 0xca, val 0x0 962 reg 0xcb, val 0x0 962 reg 0xcc, val 0x0 962 reg 0xcd, val 0x0 962 reg 0xce, val 0x0 962 reg 0xcf, val 0x0 962 reg 0xd0, val 0x0 962 reg 0xd1, val 0x43 962 reg 0xd2, val 0x94 962 reg 0xd3, val 0x3 962 reg 0xd4, val 0x60 962 reg 0xd5, val 0xf2 962 reg 0xd6, val 0x0 962 reg 0xd7, val 0x2 962 reg 0xd8, val 0x0 962 reg 0xd9, val 0x0 962 reg 0xda, val 0x0 962 reg 0xdb, val 0x0 962 reg 0xdc, val 0x0 962 reg 0xdd, val 0x0 962 reg 0xde, val 0x0 962 reg 0xdf, val 0x0 962 reg 0xe0, val 0x0 962 reg 0xe1, val 0x0 962 reg 0xe2, val 0x0 962 reg 0xe3, val 0x0 962 reg 0xe4, val 0x0 962 reg 0xe5, val 0x0 962 reg 0xe6, val 0x0 962 reg 0xe7, val 0x0 962 reg 0xe8, val 0x0 962 reg 0xe9, val 0x0 962 reg 0xea, val 0x0 962 reg 0xeb, val 0x0 962 reg 0xec, val 0x0 962 reg 0xed, val 0x0 962 reg 0xee, val 0x0 962 reg 0xef, val 0x0 962 reg 0xf0, val 0x5f 962 reg 0xf1, val 0x55 962 reg 0xf2, val 0x42 962 reg 0xf3, val 0x39 962 reg 0xf4, val 0x36 962 reg 0xf5, val 0x30 962 reg 0xf6, val 0x0 962 reg 0xf7, val 0x0 962 reg 0xf8, val 0x0 962 reg 0xf9, val 0x0 962 reg 0xfa, val 0x0 962 reg 0xfb, val 0x0 962 reg 0xfc, val 0x0 962 reg 0xfd, val 0x0 962 reg 0xfe, val 0x0 962 reg 0xff, val 0x0 935 reg 0x0, val 0x30 935 reg 0x1, val 0x0 935 reg 0x2, val 0x73 935 reg 0x3, val 0x48 935 reg 0x4, val 0x0 935 reg 0x5, val 0x3 935 reg 0x6, val 0x43 935 reg 0x7, val 0x7d 935 reg 0x8, val 0xfe 935 reg 0x9, val 0x1e 935 reg 0xa, val 0x10 935 reg 0xb, val 0x7f 935 reg 0xc, val 0x7f 935 reg 0xd, val 0x28 935 reg 0xe, val 0xa5 935 reg 0xf, val 0x0 935 reg 0x10, val 0x0 935 reg 0x11, val 0x0 935 reg 0x12, val 0x0 935 reg 0x13, val 0x0 935 reg 0x14, val 0x0 935 reg 0x15, val 0x20 935 reg 0x16, val 0x18 935 reg 0x17, val 0x3c 935 reg 0x18, val 0x80 935 reg 0x19, val 0x62 935 reg 0x1a, val 0x62 935 reg 0x1b, val 0x62 935 reg 0x1c, val 0x0 935 reg 0x1d, val 0x0 935 reg 0x1e, val 0x0 935 reg 0x1f, val 0x0 935 reg 0x20, val 0x0 935 reg 0x21, val 0x0 935 reg 0x22, val 0x0 935 reg 0x23, val 0x0 935 reg 0x24, val 0x0 935 reg 0x25, val 0x2 935 reg 0x26, val 0x0 935 reg 0x27, val 0x0 935 reg 0x28, val 0x67 935 reg 0x29, val 0x33 935 reg 0x2a, val 0x1 935 reg 0x2b, val 0x0 935 reg 0x2c, val 0x0 935 reg 0x2d, val 0x0 935 reg 0x2e, val 0x0 935 reg 0x2f, val 0x0 935 reg 0x30, val 0x0 935 reg 0x31, val 0x20 935 reg 0x32, val 0x9 935 reg 0x33, val 0x4 935 reg 0x34, val 0x0 935 reg 0x35, val 0x11 935 reg 0x36, val 0x0 935 reg 0x37, val 0x60 935 reg 0x38, val 0x0 935 reg 0x39, val 0x0 935 reg 0x3a, val 0x0 935 reg 0x3b, val 0x0 935 reg 0x3c, val 0x0 935 reg 0x3d, val 0x0 935 reg 0x3e, val 0x0 935 reg 0x3f, val 0x0 935 reg 0x40, val 0x0 935 reg 0x41, val 0x0 935 reg 0x42, val 0x0 935 reg 0x43, val 0x0 935 reg 0x44, val 0x0 935 reg 0x45, val 0x0 935 reg 0x46, val 0x0 935 reg 0x47, val 0x0 935 reg 0x48, val 0x0 935 reg 0x49, val 0x0 935 reg 0x4a, val 0x0 935 reg 0x4b, val 0x0 935 reg 0x4c, val 0x0 935 reg 0x4d, val 0x0 935 reg 0x4e, val 0x0 935 reg 0x4f, val 0x0 935 reg 0x50, val 0x20 935 reg 0x51, val 0xc0 935 reg 0x52, val 0x45 935 reg 0x53, val 0x5 935 reg 0x54, val 0x0 935 reg 0x55, val 0x0 935 reg 0x56, val 0x0 935 reg 0x57, val 0x0 935 reg 0x58, val 0x7 935 reg 0x59, val 0x7 935 reg 0x5a, val 0x7 935 reg 0x5b, val 0x0 935 reg 0x5c, val 0x0 935 reg 0x5d, val 0x0 935 reg 0x5e, val 0x0 935 reg 0x5f, val 0x0 935 reg 0x60, val 0x0 935 reg 0x61, val 0x0 935 reg 0x62, val 0x0 935 reg 0x63, val 0x0 935 reg 0x64, val 0x0 935 reg 0x65, val 0x88 935 reg 0x66, val 0x0 935 reg 0x67, val 0x0 935 reg 0x68, val 0x0 935 reg 0x69, val 0x0 935 reg 0x6a, val 0x0 935 reg 0x6b, val 0x0 935 reg 0x6c, val 0x0 935 reg 0x6d, val 0x0 935 reg 0x6e, val 0x0 935 reg 0x6f, val 0x0 935 reg 0x70, val 0x0 935 reg 0x71, val 0x0 935 reg 0x72, val 0x25 935 reg 0x73, val 0x0 935 reg 0x74, val 0x0 935 reg 0x75, val 0x0 935 reg 0x76, val 0x0 935 reg 0x77, val 0x0 935 reg 0x78, val 0x0 935 reg 0x79, val 0x0 935 reg 0x7a, val 0xe4 935 reg 0x7b, val 0x0 935 reg 0x7c, val 0x0 935 reg 0x7d, val 0x0 935 reg 0x7e, val 0x0 935 reg 0x7f, val 0x0 935 reg 0x80, val 0x0 935 reg 0x81, val 0x0 935 reg 0x82, val 0x0 935 reg 0x83, val 0x0 935 reg 0x84, val 0x0 935 reg 0x85, val 0x0 935 reg 0x86, val 0x90 935 reg 0x87, val 0x0 935 reg 0x88, val 0x0 935 reg 0x89, val 0x0 935 reg 0x8a, val 0x0 935 reg 0x8b, val 0x0 935 reg 0x8c, val 0x4 935 reg 0x8d, val 0x0 935 reg 0x8e, val 0x0 935 reg 0x8f, val 0x0 935 reg 0x90, val 0x32 935 reg 0x91, val 0xe3 935 reg 0x92, val 0x64 935 reg 0x93, val 0x1 935 reg 0x94, val 0x0 935 reg 0x95, val 0x0 935 reg 0x96, val 0x0 935 reg 0x97, val 0x0 935 reg 0x98, val 0x0 935 reg 0x99, val 0x0 935 reg 0x9a, val 0x26 935 reg 0x9b, val 0x0 935 reg 0x9c, val 0x6 935 reg 0x9d, val 0x0 935 reg 0x9e, val 0x0 935 reg 0x9f, val 0xe 935 reg 0xa0, val 0x0 935 reg 0xa1, val 0xd 935 reg 0xa2, val 0xe 935 reg 0xa3, val 0xc 935 reg 0xa4, val 0xc 935 reg 0xa5, val 0x10 935 reg 0xa6, val 0x42 935 reg 0xa7, val 0x10 935 reg 0xa8, val 0x10 935 reg 0xa9, val 0x10 935 reg 0xaa, val 0x3 935 reg 0xab, val 0x1 935 reg 0xac, val 0x0 935 reg 0xad, val 0x0 935 reg 0xae, val 0x0 935 reg 0xaf, val 0x0 935 reg 0xb0, val 0x4 935 reg 0xb1, val 0x4a 935 reg 0xb2, val 0x3f 935 reg 0xb3, val 0x0 935 reg 0xb4, val 0x0 935 reg 0xb5, val 0x0 935 reg 0xb6, val 0x0 935 reg 0xb7, val 0x0 935 reg 0xb8, val 0x0 935 reg 0xb9, val 0x0 935 reg 0xba, val 0x0 935 reg 0xbb, val 0x0 935 reg 0xbc, val 0x0 935 reg 0xbd, val 0x0 935 reg 0xbe, val 0x0 935 reg 0xbf, val 0x0 935 reg 0xc0, val 0x0 935 reg 0xc1, val 0x0 935 reg 0xc2, val 0x0 935 reg 0xc3, val 0x0 935 reg 0xc4, val 0x0 935 reg 0xc5, val 0x0 935 reg 0xc6, val 0x0 935 reg 0xc7, val 0x0 935 reg 0xc8, val 0x0 935 reg 0xc9, val 0x0 935 reg 0xca, val 0x0 935 reg 0xcb, val 0x0 935 reg 0xcc, val 0x0 935 reg 0xcd, val 0x0 935 reg 0xce, val 0x0 935 reg 0xcf, val 0x0 935 reg 0xd0, val 0x0 935 reg 0xd1, val 0x0 935 reg 0xd2, val 0x0 935 reg 0xd3, val 0x0 935 reg 0xd4, val 0x0 935 reg 0xd5, val 0x0 935 reg 0xd6, val 0x0 935 reg 0xd7, val 0x0 935 reg 0xd8, val 0x0 935 reg 0xd9, val 0x0 935 reg 0xda, val 0x0 935 reg 0xdb, val 0x0 935 reg 0xdc, val 0x0 935 reg 0xdd, val 0x0 935 reg 0xde, val 0x0 935 reg 0xdf, val 0x0 935 reg 0xe0, val 0x0 935 reg 0xe1, val 0x0 935 reg 0xe2, val 0x0 935 reg 0xe3, val 0x0 935 reg 0xe4, val 0x0 935 reg 0xe5, val 0x0 935 reg 0xe6, val 0x0 935 reg 0xe7, val 0x0 935 reg 0xe8, val 0x0 935 reg 0xe9, val 0x0 935 reg 0xea, val 0x0 935 reg 0xeb, val 0x0 935 reg 0xec, val 0x0 935 reg 0xed, val 0x0 935 reg 0xee, val 0x0 935 reg 0xef, val 0x0 935 reg 0xf0, val 0x5f 935 reg 0xf1, val 0x55 935 reg 0xf2, val 0x42 935 reg 0xf3, val 0x39 935 reg 0xf4, val 0x35 935 reg 0xf5, val 0x33 935 reg 0xf6, val 0x0 935 reg 0xf7, val 0x0 935 reg 0xf8, val 0x0 935 reg 0xf9, val 0x0 935 reg 0xfa, val 0x0 935 reg 0xfb, val 0x0 935 reg 0xfc, val 0x0 935 reg 0xfd, val 0x0 935 reg 0xfe, val 0x0 935 reg 0xff, val 0x0