Hi,

Requesting your comment on routing of DOUT+ and DOUT- incase of single ended solution

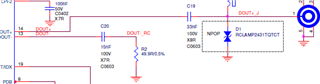

Our schematic snippet:

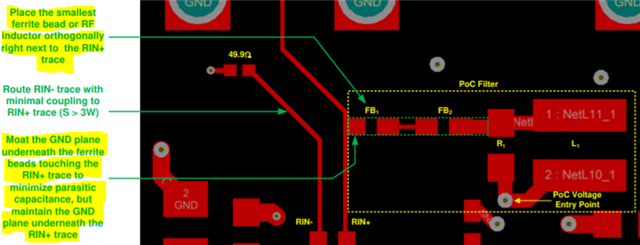

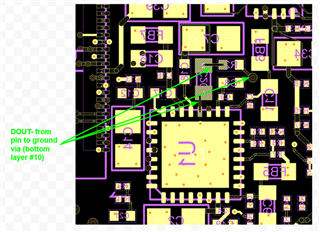

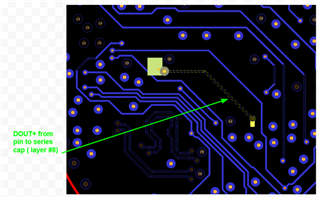

In the layout the traces are routed separately:

DOUT- between serializer pin 13 and via to GND (bottom layer)

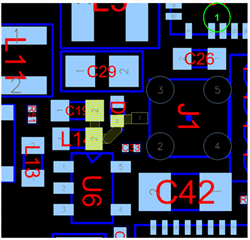

DOUT+ from serializer pin 14, via to layer 8 (with impedance control at 50ohm) and to via to the top layer.

DOUT+ AC cap (c19) to coax connector J1 (top layer)

Please review it.

thanks,

amotz