Hello,

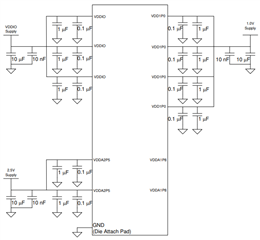

We have a custom design with DP83867IS and ZynqMPSOC - SGMII. Please refer the attached schematic.

In some of the boards one in every 10 power cycles, we didn't see the PHY, until we go for next power cycle.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

We have a custom design with DP83867IS and ZynqMPSOC - SGMII. Please refer the attached schematic.

In some of the boards one in every 10 power cycles, we didn't see the PHY, until we go for next power cycle.

Hi Srinivas,

Can you clarify what you mean by "we didn't see the PHY"? Is the PHY not powering on, or is there no link detected? Can you probe RX_CLK and CLKOUT to see if they are present?

This could possibly be a POR timing issue. Can you confirm your supply ramps meet the datasheet requirements? This could also possibly be a strap contention issue. Can you share your schematic for review?

Thanks,

Lucas

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).

Hi Lucas,

Thanks for the reply.

"we didn't see the PHY" - I meant, processor didn't detect the PHY. It was powered on. The processor could able to detect only after a power cycle.

I will share the captures later today. I had shared the schematic - attaching here again.

Thanks,

Srinivas

Hi Srinivas,

My apologies, I didn't see the attachment in your original post. I'm reviewing your schematic and will provide feedback by Wednesday.

Thanks,

Lucas

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).

Hi Srinivas,

Here are my notes after reviewing your schematic:

This seems like a POR issue, so I recommend trying the reset network to see if this works. Can you share a diagram of supply ramps including reset? Can you read registers in both the working and nonworking cases?

Thanks,

Lucas

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).

Hi Srinivas,

We recommend leaving the JTAG pins floating as opposed to pulling them down.

Thanks,

Lucas

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).

Hi Lucas,

Thanks for the comments .I will go through and let you know the observations.

A quick update - adding a reset from Processor to PHY, after power-up we are not seeing the issue. We didn't implement the reset in software as the PHY datasheet didn't say it is a mandatory.

Regards,

Srinivas

Hi Srinivas,

Can you share a supply ramp diagram including the reset line?

Thanks,

Lucas

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).

Hi Lucas,

Please see below. Yellow: +3.3V_ETH and Green: RESET_N

Thanks,

Srinivas

Hi Srinivas,

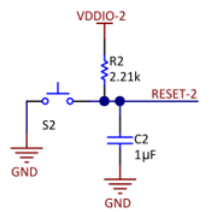

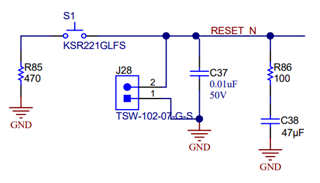

Can you share an image with all supplies individually ramping as well as reset? It seems like since a reset is needed after powerup, reset is not rising after all supplies have ramped. Can you try the following RC network on the reset pin?

Thanks,

Lucas

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).

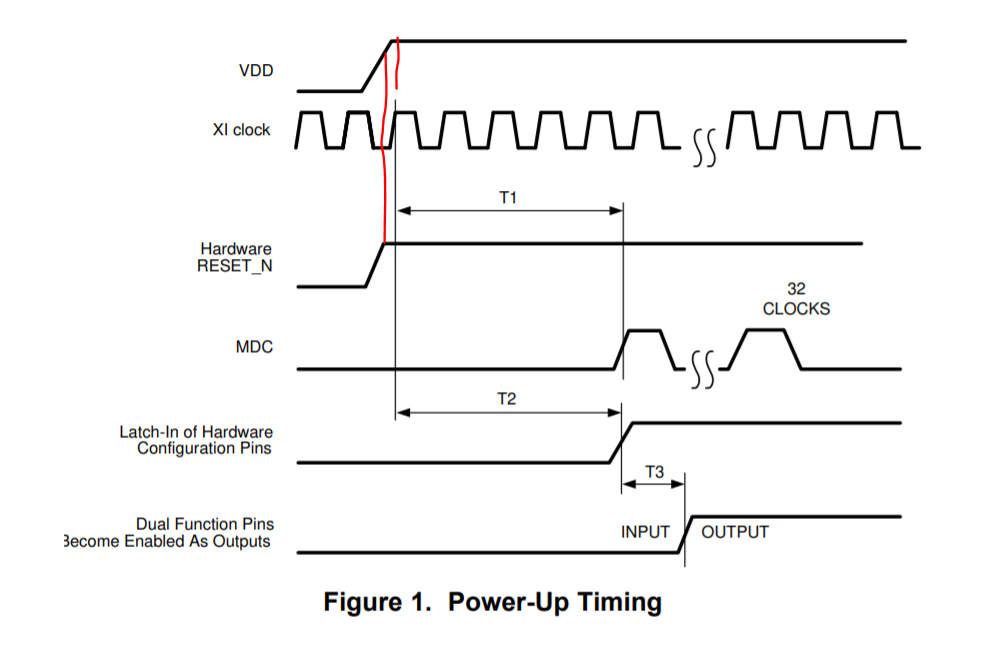

Hi Lucas,

As the POR is generated by PHY itself I believe the reset captured on the board doesn't represent the POR generated by the PHY.

As the RESET_N pin has the pull up on the board, it is raising along with +3.3V_ETH.

Please see below power-up timing from the datasheet. It doesn't give any info on the POR.

Thanks,

Srinivas

Hi Srinivas,

Delaying reset using the processor will make your power up sequence more robust, is this feasible given your setup?

Thanks,

Lucas

All information in this correspondence and in any related correspondence is provided “as is” and “with all faults”, and it is subject to TI’s Important Notice (http://www.ti.com/corp/docs/legal/important-notice.shtml).