Other Parts Discussed in Thread: USB-2-MDIO

Hi team,

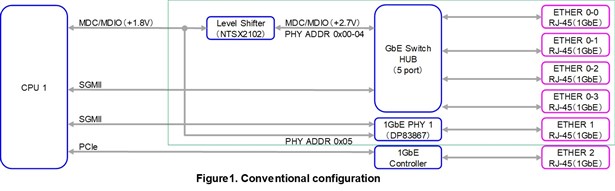

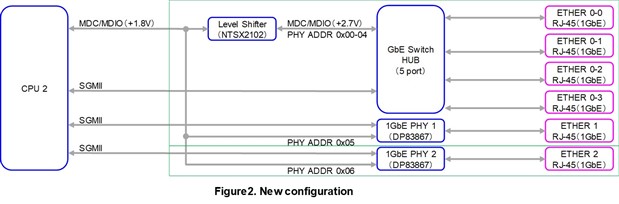

Our customer use this device follow constitutions.

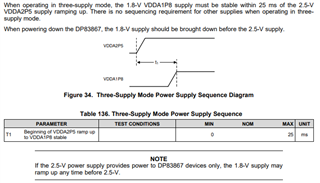

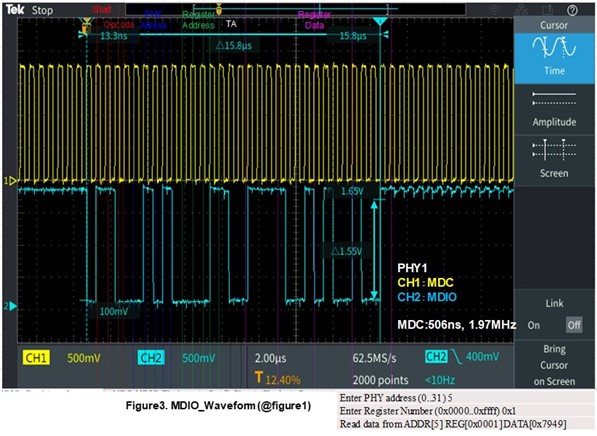

In figure1, we can observe accessing to register of DP83867. Figure3 show the MDIO Register Access at figure1.

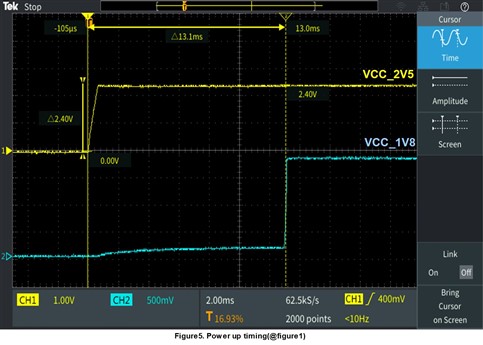

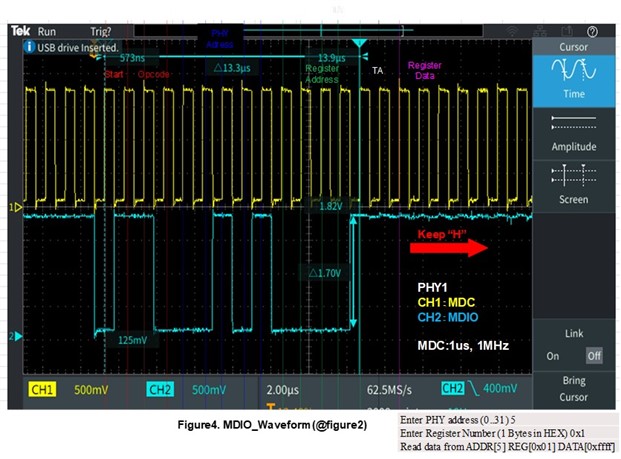

But, in figure2, we can't observe accessing to register of DP83867 at PHY1. Figure4 show the MDIO Register Access at figure2 PHY1.

In figure4, Register Data is 0xffff.

And the customer checked follow.

・Config Pin : Strap Configuration waveforms is same when the Reset signal is released in figure1 and figure2

・Clock : The CLK signal to PHY is same in figure1 and figure2.

Please let me know any causes of this matter.

Best regards,

teritama