Hi!

We will run RGMII, 10 Mbps mode from MAC towards the PHY.

I want the DP83TD510E PHY to insert a delay on the input TX clock (TXC).

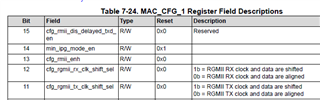

Question 1. I can see where we enable the delay insertion:

I find the description text ambigious. It seems to me that the text "1b = RGMII TX clock and data are shifted" can be interpreted in two ways:

The TX clock is already delayed by the transmitter or PCB when it arrives to the PHY.

or

The TX clock is delayed by the PHY.

So, do we write '1' or '0' to enable TXC delay in the PHY?

Question 2.

If we enable TXC delay, how much delay is added? If configurable, which register is it?

Question 3.

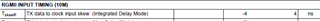

In the DP83TD510E data sheet, for 10M RGMII input, it says TskewR = from [-4 to 4] ns.

Does these numbers assume that PHY inserts no delay on the TX clk? In other words, if PHY is set to insert a 2 ns delay, the TskewR increases to [-2 to 6] ns?

Since TskewR is not illustrated in any figure in the data sheet, I am basing my understanding of TskewR on the RGMII 2.0 spec.

(It seems to me that we should aim for a positive minimum TskewR, so that the received TXC always arrives _after_ the data goes valid... And this can be achieved by increasing the delay added to the TX clk...)