Part Number: DP83867E

Hello, we have a DP83867E connected with 4-wire SGMII to a Marvell PHY. The PHY is powered and we have access to the MDI interface and can read its registers, but we can't establish a SGMII link.

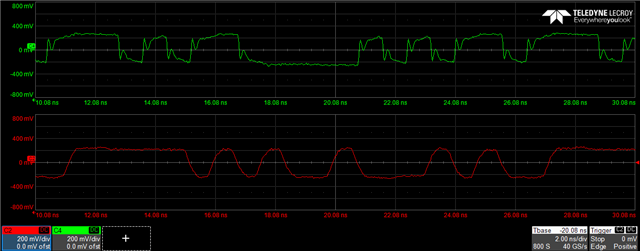

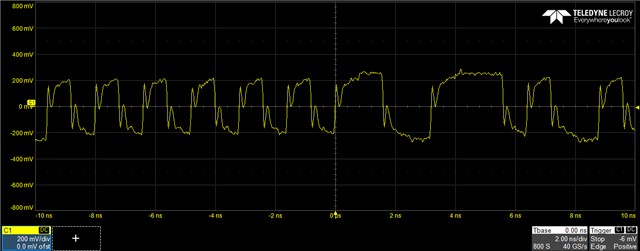

On the PHY->Marvell side, the SGMII signal quality looks as expected. On the Marvell->PHY side, there are massive reflections, see image.

There are no strap resistors on the SGMII_SIN/P or SGMII_SON/P signals. Each differential wire has a 0.1uF capacitor in series (placed next to the PHY on the offending line). The differential signal is routed with 100 Ohm impedance, following the guidelines in the DP83867E SGMII troubleshooting guide.

When measured without the PHY (removed the capacitors and replaced with a 100Ohm termination resistor), the signal from the Marvell PHY all the way up to the capacitor pads next to the PHY was of good quality.

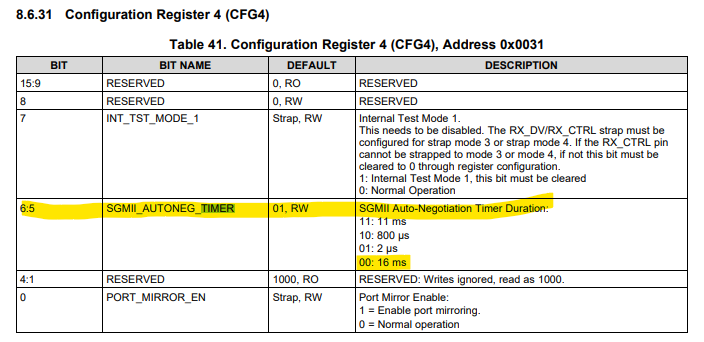

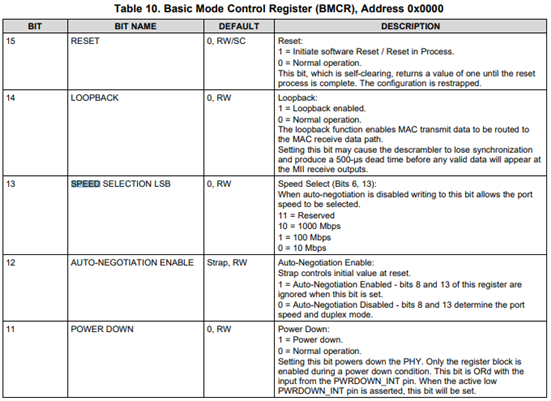

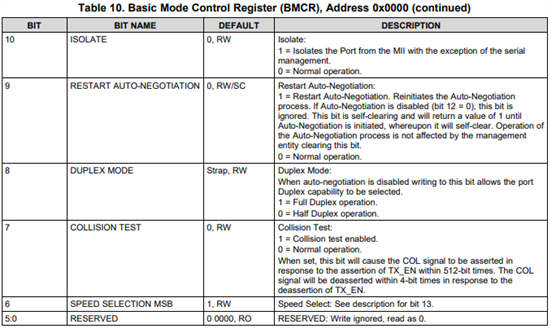

Any suggestions on how to continue debugging? Any register values that could be of use?