Other Parts Discussed in Thread: ALP

Hi,

I am studying 92x products recently, and I want to transfer I2S signal through FPD-Link.

I use 924EVM and 927EVM pair to transmit i2s signal through FPD-link, but I can't get the SCLK signal from 924 side.

I have successfully received WC and data signal in 924 side except SCLK, though I use the same configuration for the related pins.

I have checked the sclk waveform in 927 side which is OK, but no waveform shows in CLK pin in 924.

WC and DATA signals show in both side are the same and correct.

Could please help solve such problems?

Thanks.

The following is my configuration for 924

Register Display - ALP Nano 1 - DS90UB924, Connector 1

Register Data Name

0x0000 0x58 I2C Device ID

0x0001 0x04 Reset

0x0002 0x00 General Configuration 0

0x0003 0xF0 General Configuration 1

0x0004 0xFE BCC Watchdog Control

0x0005 0x1E I2C Control 1

0x0006 0x00 I2C Control 2

0x0007 0x36 Remote ID

0x0008 0x00 SlaveID[0]

0x0009 0x00 SlaveID[1]

0x000A 0x00 SlaveID[2]

0x000B 0x00 SlaveID[3]

0x000C 0x00 SlaveID[4]

0x000D 0x00 SlaveID[5]

0x000E 0x00 SlaveID[6]

0x000F 0x00 SlaveID[7]

0x0010 0x00 SlaveAlias[0]

0x0011 0x00 SlaveAlias[1]

0x0012 0x00 SlaveAlias[2]

0x0013 0x00 SlaveAlias[3]

0x0014 0x00 SlaveAlias[4]

0x0015 0x00 SlaveAlias[5]

0x0016 0x00 SlaveAlias[6]

0x0017 0x00 SlaveAlias[7]

0x0018 0x00 Mailbox[0]

0x0019 0x01 Mailbox[1]

0x001B 0xF4 Frequency Counter

0x001C 0x03 General Status

0x001D 0x25 GPIO0 Config

0x001E 0x55 GPIO1 and GPIO2 Configuration

0x001F 0x00 GPIO3 Configuration

0x0020 0x00 GPIO_REG5 and GPIO_REG6 Configuration

0x0021 0x22 GPIO_REG7 and GPIO_REG8 Configuration

0x0022 0x52 Data Path Control

0x0023 0x10 Rx Mode Status

0x0024 0x08 BIST Control

0x0025 0x00 BIST Error

0x0026 0x83 SCL High Time

0x0027 0x84 SCL Low Time

0x0028 0x00 Data Path Control 2

0x0029 0x00 FRC Control

0x002A 0x00 White Balance Control

0x002B 0x04 I2S Control

0x0035 0x00 AEQ Control

0x0039 0x00 PG Internal Clock Enable

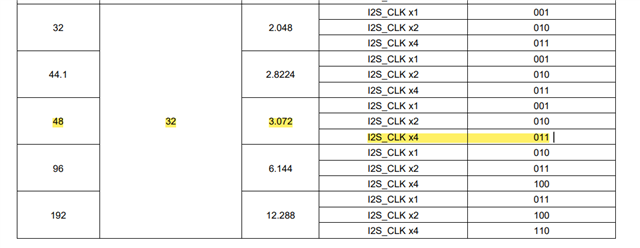

0x003A 0x00 I2S DIVSEL

0x003B 0x03 Adaptive EQ status

0x0041 0x03 Link Error Count

0x0044 0x60 Adaptive Equalizer Bypass

0x0045 0x88 Adaptive EQ MIN/MAX

0x0049 0x00 Map Select

0x004B 0x08 LVDS Setting

0x0056 0x08 Loop-Through Driver

0x0064 0x10 Pattern Generator Control

0x0065 0x00 Pattern Generator Configuration

0x0066 0x00 PGIA

0x0067 0x00 PGID

0x006E 0x00 GPI Pin Status 1

0x006F 0x00 GPI Pin Status 2

0x00F0 0x5F RX ID

0x00F1 0x55 RX ID

0x00F2 0x42 RX ID

0x00F3 0x39 RX ID

0x00F4 0x32 RX ID

0x00F5 0x38 RX ID

Regards,

Cathy