Part Number: DP83867IS

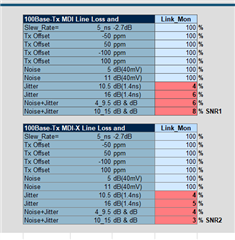

Both our design and the TI DP83867IS evaluation board exhibit failed receiver testing at 100 Mbps when jitter is introduced.

Is it possible this is the result of a register setting? The evaluation board is tested in it's power-up default state - no registers are written. On our internal design we power up and set the programmable gain register to compliance mode so the Sifos tester sees full power output when testing at 1000 Mbps - other than that - all registers are in power default states. We see the same Sifos results for the evaluation card and our design - regardless of the programmable gain register setting.