Part Number: DP83640

Other Parts Discussed in Thread: TMS570LS3137,

I want phase align master clock.

When I do the calculation according to AN-1729 application note, I get a value and call this function.

PTPClockStepAdjustment(&pObj, 0, abs(correction), FALSE);

To check if this function works I do the same thing again but correction value comes close to the first one. So I believe I cant adjust the clock.

Also after sync algorithm I do get a adjustment value but still cant adjust the clock with this function.

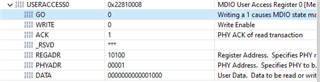

I checked the register via MDIO register of TMS570LS3137, so I confirmed that I can write the data correctly.

But after setting PTP_STEP_CLK bit of PTP_CTL register while adjusting the clock, PTP_STEP_CLK is not self clear itself eventhough the datasheet says that bit is SC.

Which steps should I follow to fix this issue?

Thanks in advance.