Part Number: TLK10034

Hello support team,

We are having problems communicating with TLK10034.

The component does not respond when we are trying to access the MDIO bus. Do you have any suggestions on what might cause this problem?

On our board the TLK10034 is powered with 1.8V and 1.0V. The 1.8V power supply is supplied first, then the 1.0V power supply .

The 156.25MHz clock is generated on the differential input REFCLK0. Then the Reset is released.

The pins MODE_SEL and ST are set to 0.

The MDC clock is continuous. It was originally at 1.8MHz, we lowered it to 1.0MHz.

The transceivers are not in Power down mode (PDTRX _N is set to 1).

There is no other PHY on MDIO interface

We are trying to access the registry PMA_DEV_IDENTIFIER_1:

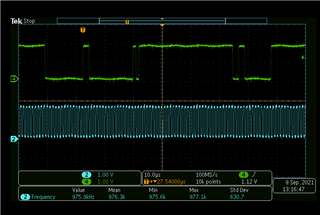

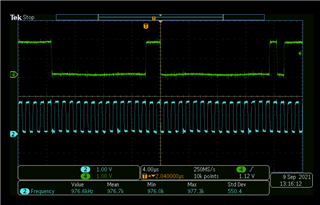

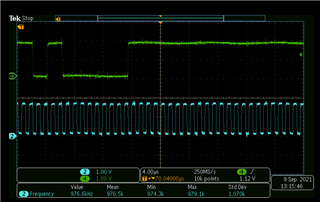

On the oscillograms below the MDC clock is on channel 2, the MDIO signal on channel 1.

On attached Pictures:

-The 2 accesses in clause 45: writing the address and reading the register

- Zoom on writing the address

-Zoom on reading the register: the component does not respond:

Best regards,

Robin